- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄97867 > DS21FT44 (MAXIM INTEGRATED PRODUCTS INC) DATACOM, FRAMER, PBGA300 PDF資料下載

參數(shù)資料

| 型號(hào): | DS21FT44 |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類: | Digital Transmission Controller |

| 英文描述: | DATACOM, FRAMER, PBGA300 |

| 封裝: | 27 X 27 MM, 1.27 MM PITCH, MCMBGA-300 |

| 文件頁數(shù): | 79/117頁 |

| 文件大?。?/td> | 691K |

| 代理商: | DS21FT44 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁當(dāng)前第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁

DS21FT44/DS21FF44

64 of 117

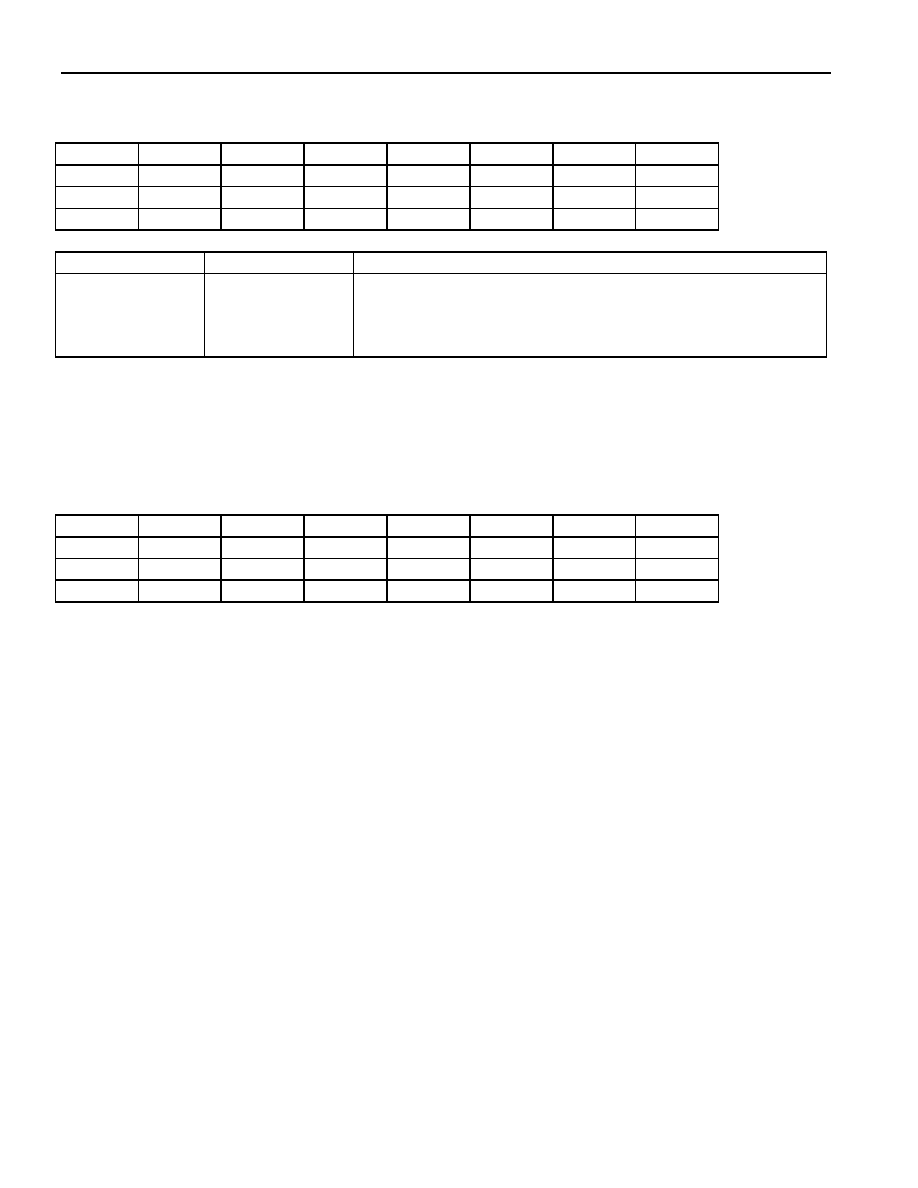

TCBR1/TCBR2/TCBR3/TCBR4: TRANSMIT CHANNEL BLOCKING REGISTERS

(Address = 22 to 25 Hex)

(MSB)

(LSB)

CH8

CH7

CH6

CH5

CH4

CH3

CH2

CH1

TCBR1 (22)

CH16

CH15

CH14

CH13

CH12

CH11

CH10

CH9

TCBR2 (23)

CH24

CH23

CH22

CH21

CH20

CH19

CH18

CH17

TCBR3 (24)

CH32

CH31

CH30

CH29

CH28

CH27

CH26

CH25

TCBR4 (25)

SYMBOL

POSITION

NAME AND DESCRIPTION

CH1–32

TCBR1.0–4.7

Transmit Channel Blocking Control Bits

0 = force the TCHBLK pin to remain low during this channel

time

1 = force the TCHBLK pin high during this channel time

Note: If CCR3.6 = 1, then a zero in the TCBRs implies that signaling data is to be sourced from TSER

(or TSIG if CCR3.2 = 1) and a one implies that signaling data for that channel is to be sourced from the

Transmit Signaling (TS) registers. See definition below.

TCBR1/TCBR2/TCBR3/TCBR4: DEFINITION WHEN CCR3.6 = 1

(MSB)

(LSB)

CH20

CH4

CH19

CH3

CH18

CH2

CH17*

CH1*

TCBR1 (22)

CH24

CH8

CH23

CH7

CH22

CH6

CH21

CH5

TCBR2 (23)

CH28

CH12

CH27

CH11

CH26

CH10

CH25

CH9

TCBR3 (24)

CH32

CH16

CH31

CH15

CH30

CH14

CH29

CH13

TCBR4 (25)

*CH1 and CH17 should be set to one to allow the internal TS1 register to create the CAS Multiframe Alignment Word and Spare/Remote Alarm

bits.

17.

ELASTIC STORES OPERATION

Each framer in the DS21Q44 contains dual two-frame (512 bits) elastic stores, one for the receive

direction, and one for the transmit direction. These elastic stores have two main purposes. First, they can

be used to rate convert the E1 data stream to 1.544Mbps (or a multiple of 1.544Mbps), which is the T1

rate. Secondly, they can be used to absorb the differences in frequency and phase between the E1 data

stream and an asynchronous (i.e., not frequency locked) backplane clock, which can be 1.544MHz or

2.048MHz. The backplane clock can burst at rates up to 8.192MHz. Both elastic stores contain full

controlled slip capability, which is necessary for this second purpose. Both elastic stores within a framer

are fully independent and no restrictions apply to the sourcing of the various clocks that are applied to

them. The transmit side elastic store can be enabled whether the receive elastic store is enabled or

disabled and vice versa. Also, each elastic store can interface to either a 1.544MHz or 2.048MHz

backplane without regard to the backplane rate the other elastic store is interfacing.

Two mechanisms are available to the user for resetting the elastic stores. The Elastic Store Reset (CCR6.0

and CCR6.1) function forces the elastic stores to a depth of one frame unconditionally. Data is lost during

the reset. The second method, the Elastic Store Align (CCR5.5 and CCR5.6) forces the elastic store depth

to a minimum depth of half a frame only if the current pointer separation is already less then half a frame.

If a realignment occurs data is lost. In both mechanisms, independent resets are provided for both the

receive and transmit elastic stores.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS21Q352 | DATACOM, PCM TRANSCEIVER, PBGA256 |

| DS21Q354 | DATACOM, PCM TRANSCEIVER, PBGA256 |

| DS21Q41BT | DATACOM, FRAMER, PQFP128 |

| DS21Q42TN | DATACOM, FRAMER, PQFP128 |

| DS21Q42T | DATACOM, FRAMER, PQFP128 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS21FT44+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 4X3 E1 Framer E1 Framer E1 Framer RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS21FT44N | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 4x4 16/4x3 12 Chnl E1/E1 Framer RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS21FT44N+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 4x4 16/4x3 12 Chnl E1/E1 Framer RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS21Q348 | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS21Q348B | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。