- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄97868 > DS2151Q (DALLAS SEMICONDUCTOR) DATACOM, FRAMER, PQCC44 PDF資料下載

參數(shù)資料

| 型號(hào): | DS2151Q |

| 廠商: | DALLAS SEMICONDUCTOR |

| 元件分類: | Digital Transmission Controller |

| 英文描述: | DATACOM, FRAMER, PQCC44 |

| 封裝: | PLASTIC, LCC-44 |

| 文件頁(yè)數(shù): | 25/47頁(yè) |

| 文件大小: | 413K |

| 代理商: | DS2151Q |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)當(dāng)前第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)

MAX1464

Low-Power, Low-Noise Multichannel

Sensor Signal Processor

31

Maxim Integrated

SE[3:0]

PGA

RANGE (V/V)

ADC

+INPUT

ADC

-INPUT

DESCRIPTION

0001

0.99

VBG

VSS

Bandgap voltage.

0010

0.99 to 244

OUTnSM

VSS

Output of small op-amp n.

0011

0.99 to 244

OUTnLG

VSS

Output of large op-amp n.

0100

0.7*

VDD**

VSS

Power-supply voltage.

0101

0.7*

VSS

Power-supply ground.

0110

0.7*

DACn_OUT using

OUTnSM

VSS

DACn output through small op-amp n configured

as unity-gain buffer.

0111

0.7*

DACn_OUT using

OUTnLG

VSS

DACn output through large op-amp n configured

as unity-gain buffer.

1000

0.99 to 244

INPn

VSS

Single-ended input on INPn.

1001

0.99 to 244

INMn

VSS

Single-ended input on INMn.

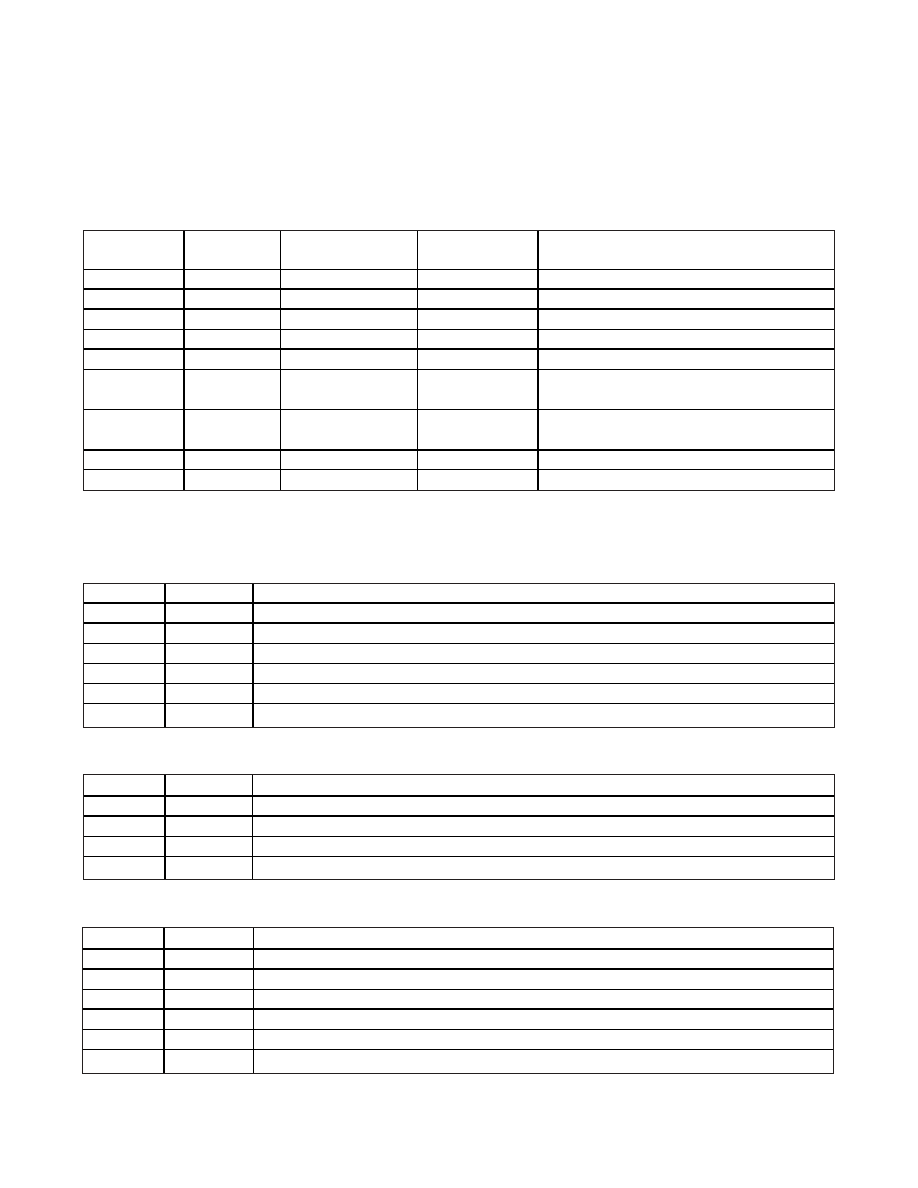

Table 7. Single-Ended (SE[3:0])

*

The PGA operates at a fixed reduced gain of 0.7V/V to enable conversion of input signals at and near VDD and VSS. This gain set-

ting is not selectable.

**

When measuring VDD, use the external reference or the 4 x VBG setting.

BIT

NAME

DESCRIPTION

15–11

PGA1[4:0]

Programmable-gain amplifier setting to use during conversion of channel 1. PGA1[4] = MSB.

10–8

CLK1[2:0]

ADC clock setting to use during conversion of channel 1. CLK1[2] = MSB.

7

—

Unused.

6–4

RES1[2:0]

ADC resolution setting to use during conversion of channel 1. RES1[2] = MSB.

3

CO1[3]

Coarse-offset sign bit.

2–0

CO1[2:0]

Coarse-offset DAC setting to use during conversion of channel 1. CO1[2] = MSB.

Table 8. ADC_Config_1A (Address = 02h)

BIT

NAME

DESCRIPTION

15–7

—

Unused.

6–4

BIAS1[2:0]

ADC bias setting to use during conversion of channel 1. BIAS1[2] = MSB.

3–2

—

Unused.

1–0

REF1[1:0]

Reference select for conversion on channel 1. REF1[1] = MSB.

Table 9. ADC_Config_1B (Address = 03h)

BIT

NAME

DESCRIPTION

15–11

PGA2[4:0]

Programmable-gain amplifier to use during conversion of channel 2. PGA[4] = MSB.

10–8

CLK2[2:0]

ADC clock setting to use during conversion of channel 2. CLK2[2] = MSB.

7

—

Unused.

6

RES2[2:0]

ADC resolution setting to use during conversion of channel 2. RES2[2] = MSB.

3

CO2[3]

Coarse-offset DAC sign bit.

2–0

CO2[2:0]

Coarse-offset DAC setting to use during conversion of channel 2. CO2[2] = MSB.

Table 10. ADC_Config_2A (Address = 05h)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS229S | LINE TRANSCEIVER, PDSO20 |

| DS232AE | LINE TRANSCEIVER, PDSO20 |

| DS232AR | LINE TRANSCEIVER, PDSO16 |

| DS232AR-N | LINE TRANSCEIVER, PDSO16 |

| DS232AS-N | LINE TRANSCEIVER, PDSO16 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS2151Q/T&R | 制造商:Maxim Integrated Products 功能描述:IC TXRX T1 1-CHIP 5V LP 44-PLCC |

| DS2151Q/T&R | 功能描述:IC TXRX T1 1-CHIP 5V LP 44-PLCC RoHS:否 類別:集成電路 (IC) >> 接口 - 電信 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS 產(chǎn)品變化通告:Product Discontinuation 06/Feb/2012 標(biāo)準(zhǔn)包裝:750 系列:* |

| DS2151QB | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS2151QB/T&R | 制造商:Maxim Integrated Products 功能描述:T1 SINGLE CHIP XCVR REV B T&R - Tape and Reel |

| DS2151QB/T&R+ | 制造商:Maxim Integrated Products 功能描述:FRAMER DS1/E1/ISDN-PRI/T1 5V 44PLCC - Tape and Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。