- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄378536 > DDC114EH (Diodes Inc.) NPN PRE-BIASED SMALL SIGNAL SOT-563 DUAL SURFACE MOUNT TRANSISTOR PDF資料下載

參數(shù)資料

| 型號(hào): | DDC114EH |

| 廠商: | Diodes Inc. |

| 英文描述: | NPN PRE-BIASED SMALL SIGNAL SOT-563 DUAL SURFACE MOUNT TRANSISTOR |

| 中文描述: | npn型預(yù)偏置信號(hào)小的SOT - 563雙表面貼裝晶體管 |

| 文件頁(yè)數(shù): | 22/30頁(yè) |

| 文件大?。?/td> | 389K |

| 代理商: | DDC114EH |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)當(dāng)前第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)

""#

SBAS255A JUNE 2004 REVISED NOVEMBER 2004

SPECIAL CONSIDERATIONS

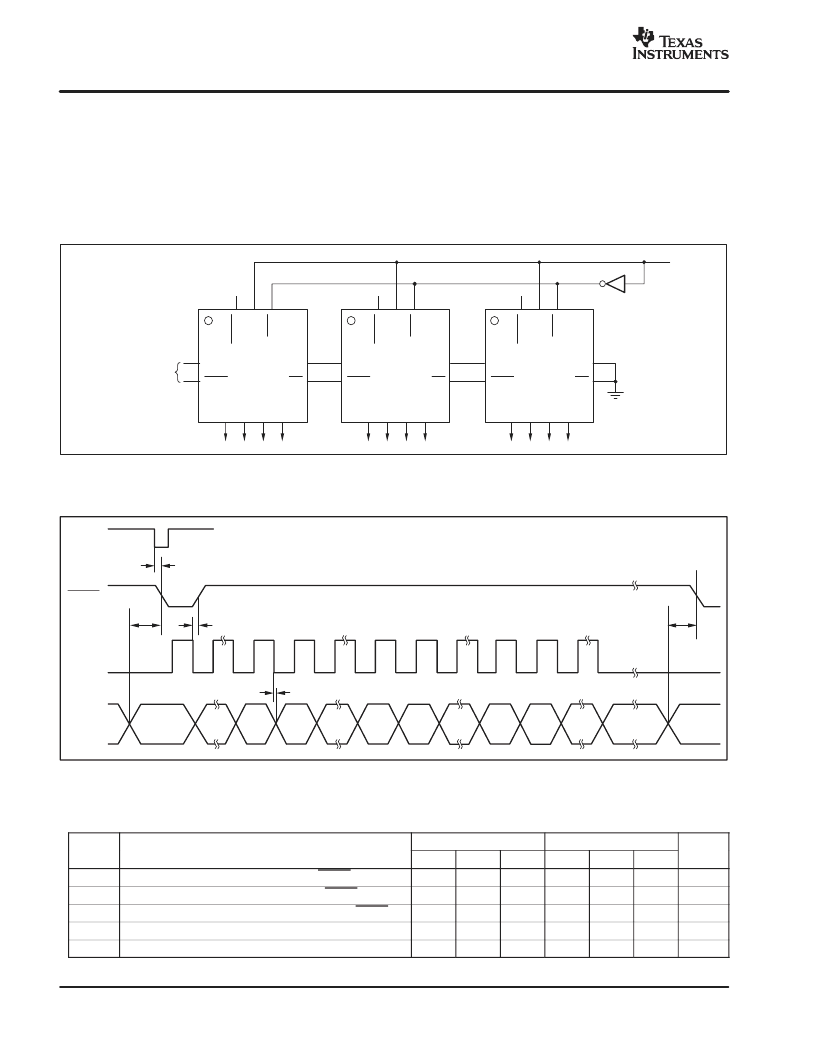

Cascading Multiple Converters

Multiple DDC114 units can be connected in serial

configuration, as illustrated in Figure 20.

www.ti.com

22

DOUT can be used with DIN to daisy-chain several

DDC114 devices together to minimize wiring. In this mode

of operation, the serial data output is shifted through

multiple DDC114s, as illustrated in Figure 20.

See Figure 22 for the timing diagram when the DIN

function is used to daisy-chain several devices. Table 11

gives the timing specification for data retrieval using DIN.

I

I

I

I

A

Sensor

B

C

D

DIN

DIN

DOUT

DOUT

DDC114

DIN

DIN

DOUT

DOUT

DIN

DIN

DOUT

DOUT

D

D

D

Data Retrievel

Outputs

D

D

D

D

D

D

I

I

I

I

E

F

G

H

DDC114

I

I

I

I

I

J

K

L

DDC114

Data Clock

Figure 20. Daisy-Chained DDC114s

CLK

DVALID

DCLK

DOUT

t

18

t

19

t

21

t

20

Input 4

MSB

Input 1

LSB

Input 4

LSB

Input 3

MSB

Input 3

LSB

Input 2

MSB

Input 2

LSB

Input 1

MSB

Input 4

MSB

t

20

Figure 21. Digital Interface Timing Diagram for Data Retrieval From a Single DDC114

Table 10. Timing for the DDC114 Data Retrieval

SYMBOL

DESCRIPTION

CLK = 4MHz, CLK_4X = 0

CLK = 4.8MHz, CLK_4X = 0

UNITS

MIN

TYP

MAX

MIN

TYP

MAX

t18

t19

t20

t21

Propagation Delay from Falling Edge of CLK to DVALID LOW

5

5

ns

Propagation Delay from Falling Edge of DCLK to DVALID HIGH

5

5

ns

Hold Time that DOUT is Valid Before the Falling Edge of DVALID

1.75

1.458

μ

s

Hold Time that DOUT is Valid After Falling Edge of DCLK

5

5

ns

t21A(1)

(1)

With a maximum load of one DDC114 (4pF typical) with an additional load of (5pF

).

Propagation Delay from Falling Edge of DCLK to Valid DOUT

10

10

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DDC114EH-7 | NPN PRE-BIASED SMALL SIGNAL SOT-563 DUAL SURFACE MOUNT TRANSISTOR |

| DDC114YK-7 | NPN PRE-BIASED SMALL SIGNAL SOT-26 DUAL SURFACE MOUNT TRANSISTOR |

| DDC114EK-7 | NPN PRE-BIASED SMALL SIGNAL SOT-26 DUAL SURFACE MOUNT TRANSISTOR |

| DDC114TK-7 | NPN PRE-BIASED SMALL SIGNAL SOT-26 DUAL SURFACE MOUNT TRANSISTOR |

| DDC114YH-7 | NPN PRE-BIASED SMALL SIGNAL SOT-563 DUAL SURFACE MOUNT TRANSISTOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DDC114EH-7 | 功能描述:開(kāi)關(guān)晶體管 - 偏壓電阻器 150MW 10K RoHS:否 制造商:ON Semiconductor 配置: 晶體管極性:NPN/PNP 典型輸入電阻器: 典型電阻器比率: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體: 直流集電極/Base Gain hfe Min:200 mA 最大工作頻率: 集電極—發(fā)射極最大電壓 VCEO:50 V 集電極連續(xù)電流:150 mA 峰值直流集電極電流: 功率耗散:200 mW 最大工作溫度: 封裝:Reel |

| DDC114EH-7-F | 制造商:Diodes Incorporated 功能描述:TRANS DGTL BJT NPN 100MA 6PIN SOT-563 - Tape and Reel |

| DDC114EK | 制造商:DIODES 制造商全稱:Diodes Incorporated 功能描述:NPN PRE-BIASED SMALL SIGNAL SOT-26 DUAL SURFACE MOUNT TRANSISTOR |

| DDC114EK-7 | 制造商:Diodes Incorporated 功能描述:TRANS DGTL BJT NPN 100MA 6PIN SOT-26 - Tape and Reel |

| DDC114EK-7-F | 制造商:Diodes Incorporated 功能描述:PREBIASED TRANSISTOR SOT-26 R1=R2 NPN 300MW 10KOHMS 10KOHMS - Tape and Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。