- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379101 > CYW15G0403DXB-BGXC (CYPRESS SEMICONDUCTOR CORP) Independent Clock Quad HOTLink II⑩ Transceiver PDF資料下載

參數(shù)資料

| 型號(hào): | CYW15G0403DXB-BGXC |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | Independent Clock Quad HOTLink II⑩ Transceiver |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PBGA256 |

| 封裝: | 27 X 27 MM, 1.57 MM HEIGHT, LEAD FREE, BGA-256 |

| 文件頁(yè)數(shù): | 24/45頁(yè) |

| 文件大?。?/td> | 517K |

| 代理商: | CYW15G0403DXB-BGXC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)當(dāng)前第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)

CYP15G0403DXB

CYV15G0403DXB

CYW15G0403DXB

Document #: 38-02065 Rev. *F

Page 24 of 45

JTAG Support

The CYP(V)(W)15G0403DXB contains a JTAG port to allow

system level diagnosis of device interconnect. Of the available

JTAG modes, boundary scan, and bypass are supported. This

capability is present only on the LVTTL inputs and outputs and

the REFCLKx± clock input. The high-speed serial inputs and

outputs are not part of the JTAG test chain.

To ensure valid device operation after power-up (including

non-JTAG operation), the JTAG state machine should also be

initialized to a reset state. This should be done in addition to

the device reset (using RESET). The JTAG state machine can

be initialized using TRST (asserting it LOW and de-asserting

it or leaving it asserted), or by asserting TMS HIGH for at least

5 consecutive TCLK cycles. This is necessary in order to

ensure that the JTAG controller does not enter any of the test

modes after device power-up. In this JTAG reset state, the rest

of the device will be in normal operation.

Note

. The order of device reset (using RESET) and JTAG

initialization does not matter.

3-Level Select Inputs

Each 3-Level select inputs reports as two bits in the scan

register. These bits report the LOW, MID, and HIGH state of

the associated input as 00, 10, and 11 respectively

JTAG ID

The JTAG device ID for the CYP(V)(W)15G0403DXB is

‘0C810069’x.

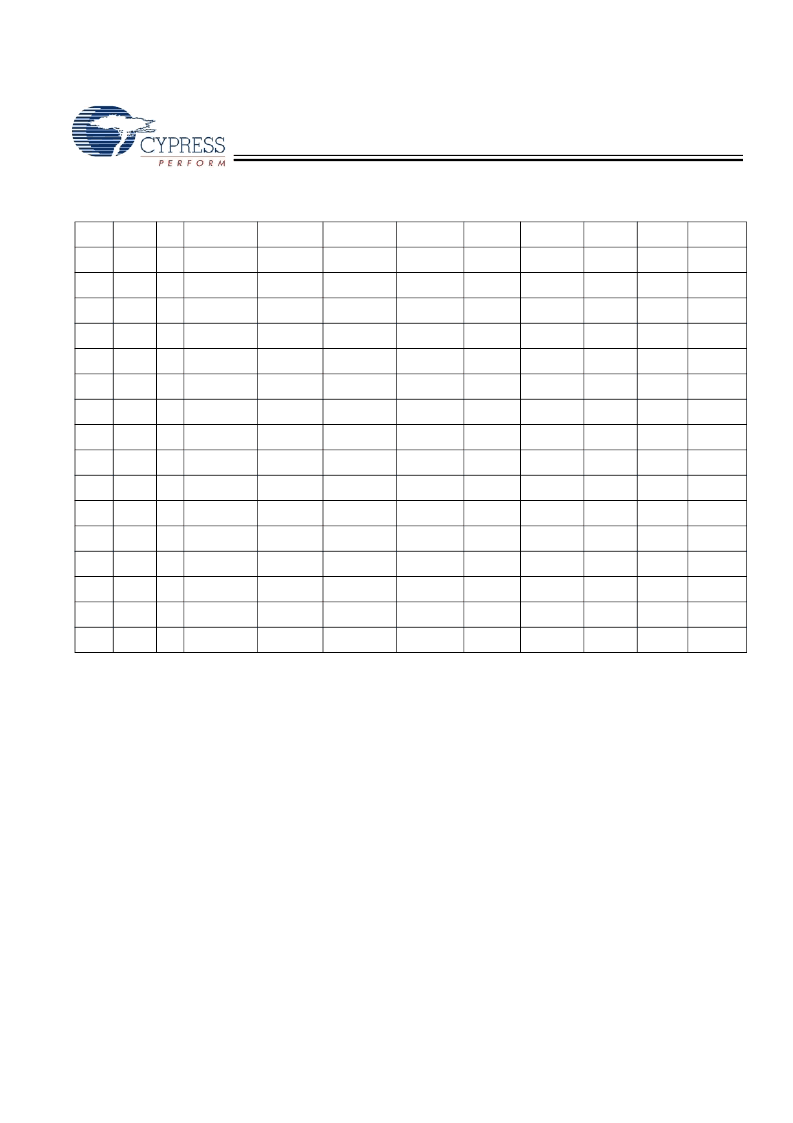

Table 10.Device Control Latch Configuration Table

ADDR

Channel Type

DATA7

DATA6

DATA5

DATA4

DATA3

DATA2

DATA1

DATA0

Reset

Value

0

(0000b)

A

S

RFMODEA[1]

RFMODEA[0]

FRAMCHARA

DECMODEA

DECBYPA

RXCKSELA

RXRATEA

GLEN0

10111111

1

(0001b)

A

S

SDASEL2A[1]

SDASEL2A[0]

SDASEL1A[1]

SDASEL1A[0]

ENCBYPA

TXCKSELA

TXRATEA

GLEN1

10101101

2

(0010b)

A

D

RFENA

RXPLLPDA

RXBISTA

TXBISTA

OE2A

OE1A

PABRSTA

GLEN2

10110011

3

(0011b)

B

S

RFMODEB[1]

RFMODEB[0]

FRAMCHARB

DECMODEB

DECBYPB

RXCKSELB

RXRATEB

GLEN3

10111111

4

(0100b)

B

S

SDASEL2B[1]

SDASEL2B[0]

SDASEL1B[1]

SDASEL1B[0]

ENCBYPB

TXCKSELB

TXRATEB

GLEN4

10101101

5

(0101b)

B

D

RFENB

RXPLLPDB

RXBISTB

TXBISTB

OE2B

OE1B

PABRSTB

GLEN5

10110011

6

(0110b)

C

S

RFMODEC[1]

RFMODEC[0]

FRAMCHARC

DECMODEC

DECBYPC

RXCKSELC

RXRATEC

GLEN6

10111111

7

(0111b)

C

S

SDASEL2C[1]

SDASEL2C[0]

SDASEL1C[1]

SDASEL1C[0]

ENCBYPC

TXCKSELC

TXRATEC

GLEN7

10101101

8

(1000b)

C

D

RFENC

RXPLLPDC

RXBISTC

TXBISTC

OE2C

OE1C

PABRSTC

GLEN8

10110011

9

(1001b)

D

S

RFMODED[1]

RFMODED[0]

FRAMCHARD

DECMODED

DECBYPD

RXCKSELD

RXRATE D

GLEN9

10111111

10

(1010b)

D

S

SDASEL2D[1]

SDASEL2D[0]

SDASEL1D[1]

SDASEL1D[0]

ENCBYPD

TXCKSELD

TXRATED

GLEN10

10101101

11

(1011b)

D

D

RFEND

RXPLLPDD

RXBISTD

TXBISTD

OE2D

OE1D

PABRSTD

GLEN11

10110011

12

(1100b)

GLOBAL

S

RFMODEGL[1]

RFMODE

GL[0]

FRAMCHARGL DECMODEGL DECBYPGL RXCKSELGL RXRATEG

L

FGLEN0

N/A

13

(1101b)

GLOBAL

S

SDASEL2GL[1]

SDASEL2GL[

0]

SDASEL1GL[1] SDASEL1GL[0

]

ENCBPGL

TXCKSELGL

TXRATEG

L

FGLEN1

N/A

14

(1110b)

GLOBAL

D

RFENGL

RXPLLPDGL

RXBISTGL

TXBISTGL

OE2GL

OE1GL

PABRSTG

L

FGLEN2

N/A

15

(1111b)

MASK

D

D7

D6

D5

D4

D3

D2

D1

D0

11111111

[+] Feedback

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CYW15G0403DXB-BGXI | Independent Clock Quad HOTLink II⑩ Transceiver |

| CYP15G0403DXB-BGI | Independent Clock Quad HOTLink II⑩ Transceiver |

| CYP15G0403DXB-BGXC | Independent Clock Quad HOTLink II⑩ Transceiver |

| CYP15G0403DXB-BGXI | Independent Clock Quad HOTLink II⑩ Transceiver |

| CYV15G0403DXB-BGC | Independent Clock Quad HOTLink II⑩ Transceiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CYW15G0403DXB-BGXI | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:Independent Clock Quad HOTLink II⑩ Transceiver |

| CYW15GO403DXB-BGI | 制造商:Cypress Semiconductor 功能描述: |

| CYW170-01SXC | 功能描述:時(shí)鐘緩沖器 133MHz Clock RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| CYW170-01SXCT | 功能描述:時(shí)鐘緩沖器 133MHz Clock RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| CYW173SXC | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 Tape Media Backup Dr Clk Gen W173 DS RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。