- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄379101 > CYP15G0403DXB-BGC (CYPRESS SEMICONDUCTOR CORP) Independent Clock Quad HOTLink II⑩ Transceiver PDF資料下載

參數(shù)資料

| 型號(hào): | CYP15G0403DXB-BGC |

| 廠(chǎng)商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類(lèi): | 通信及網(wǎng)絡(luò) |

| 英文描述: | Independent Clock Quad HOTLink II⑩ Transceiver |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PBGA256 |

| 封裝: | 27 X 27 MM, 1.57 MM HEIGHT, BGA-256 |

| 文件頁(yè)數(shù): | 30/45頁(yè) |

| 文件大小: | 517K |

| 代理商: | CYP15G0403DXB-BGC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)當(dāng)前第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)

CYP15G0403DXB

CYV15G0403DXB

CYW15G0403DXB

Document #: 38-02065 Rev. *F

Page 30 of 45

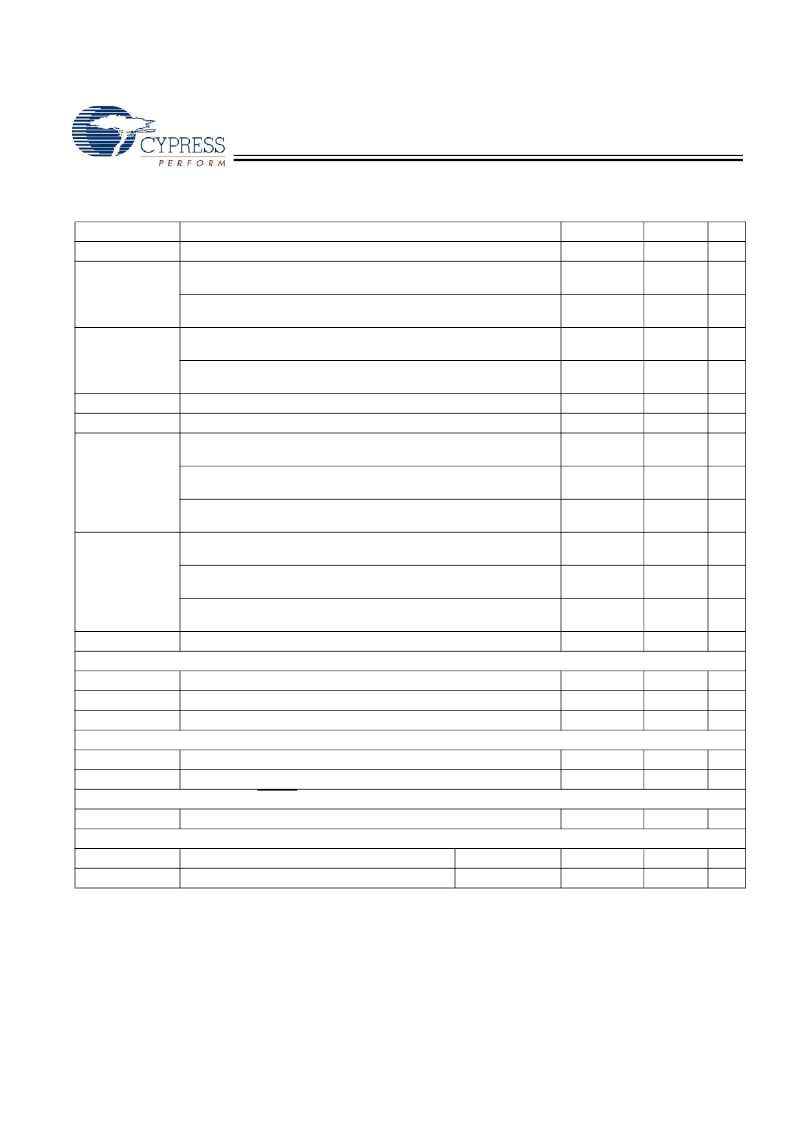

t

REFF[20, 21, 22, 23]

t

TREFDS

REFCLKx Fall Time (20%–80%)

Transmit Data Set-up Time to

REFCLKx - Full Rate

(TXRATEx = 0, TXCKSELx

=

1)

Transmit Data Set-up Time to

REFCLKx - Half Rate

(TXRATEx = 1, TXCKSELx

=

1)

Transmit Data Hold Time from REFCLKx - Full Rate

(TXRATEx = 0, TXCKSELx

=

1)

Transmit Data Hold Time from REFCLKx - Half Rate

(TXRATEx = 1, TXCKSELx

=

1)

Receive Data Access Time to

REFCLKx (RXCKSELx

=

1)

Receive Data Valid Time Window (RXCKSELx

=

1)

Received Data Valid Time to RXCLK when RXCKSELx

=

1

(TXRATEx = 0, RXRATEx = 0)

Received Data Valid Time to RXCLK when RXCKSELx

=

1

(TXRATEx = 0, RXRATEx = 1)

Received Data Valid Time to RXCLK when RXCKSELx

=

1

(TXRATEx = 1)

Received Data Valid Time from RXCLK when RXCKSELx

=

1

(TXRATEx = 0, RXRATEx = 0)

Received Data Valid Time from RXCLK when RXCKSELx

=

1

(TXRATEx = 0, RXRATEx = 1)

Received Data Valid Time from RXCLK when RXCKSELx

=

1

(TXRATEx = 1)

REFCLKx Frequency Referenced to Received Clock Period

CYP(V)(W)15G0403DXB Bus Configuration Write Timing Characteristics

Over the Operating Range

t

DATAH

Bus Configuration Data Hold

t

DATAS

Bus Configuration Data Set-up

t

WRENP

Bus Configuration WREN Pulse Width

CYP(V)(W)15G0403DXB JTAG Test Clock Characteristics

Over the Operating Range

f

TCLK

JTAG Test Clock Frequency

t

TCLK

JTAG Test Clock Period

CYP(V)(W)15G0403DXB Device RESET Characteristics

Over the Operating Range

t

RST

Device RESET Pulse Width

CYP(V)(W)15G0403DXB Transmit Serial Outputs and TX PLL Characteristics

Over the Operating Range

Parameter

Description

t

B

Bit Time

2

ns

ns

2.4

2.3

ns

t

TREFDH

1.0

ns

1.6

ns

t

RREFDA

t

RREFDW

t

REFxDV–

9.7

[28]

ns

ns

ns

10UI – 5.8

10UI

[25]

– 6.16

5UI – 2.53

[29]

ns

10UI – 5.86

[29]

ns

t

REFxDV+

1.4

ns

5UI

– 1.83

[29]

ns

1.0

[29]

ns

t

REFRX[30]

–0.15

+0.15

%

0

10

10

ns

ns

ns

20

MHz

ns

50

30

ns

Condition

Min.

5128

Max.

666

Unit

ps

Notes

28.Since this timing parameter is greater than the minimum time period of REFCLK it sets an upper limit to the frequency in which REFCLKx can be used to clock

the receive data out of the output register. For predictable timing, users can use this parameter only if REFCLK period is greater than sum of t

and set-up

time of the upstream device. When this condition is not true, RXCLKx± (a buffered or divided version of REFCLK when RXCKSELx = 1) could be used to clock

the receive data out of the device.

29.Measured using a 50% duty cycle reference clock.

30.REFCLKx has no phase or frequency relationship with the recovered clock and only acts as a centering reference to reduce clock synchronization time. REFCLKx

must be within ±1500 ppm (±0.15%) of the remote transmitter’s PLL reference (REFCLKx) frequency. Although transmitting to a HOTLink II receiver channel

necessitates the frequency difference between the transmitter and receiver reference clocks to be within ±1500 ppm, the stability of the crystal needs to be

within the limits specified by the appropriate standard when transmitting to a remote receiver that is compliant to that standard. For example, to be IEEE 802.3z

Gigabit Ethernet compliant, the frequency stability of the crystal needs to be within ±100 ppm.l.

CYP(V)(W)15G0403DXB AC Electrical Characteristics

(continued)

Parameter

Description

Min.

Max

Unit

[+] Feedback

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CYW15G0403DXB-BGXC | Independent Clock Quad HOTLink II⑩ Transceiver |

| CYW15G0403DXB-BGXI | Independent Clock Quad HOTLink II⑩ Transceiver |

| CYP15G0403DXB-BGI | Independent Clock Quad HOTLink II⑩ Transceiver |

| CYP15G0403DXB-BGXC | Independent Clock Quad HOTLink II⑩ Transceiver |

| CYP15G0403DXB-BGXI | Independent Clock Quad HOTLink II⑩ Transceiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CYP15G0403DXB-BGI | 功能描述:電信線(xiàn)路管理 IC Quad Indep Channel XCVR IND RoHS:否 制造商:STMicroelectronics 產(chǎn)品:PHY 接口類(lèi)型:UART 電源電壓-最大:18 V 電源電壓-最小:8 V 電源電流:30 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VFQFPN-48 封裝:Tray |

| CYP15G0403DXB-BGXC | 功能描述:電信線(xiàn)路管理 IC Quad Indep Ch HOTLink II XCVR RoHS:否 制造商:STMicroelectronics 產(chǎn)品:PHY 接口類(lèi)型:UART 電源電壓-最大:18 V 電源電壓-最小:8 V 電源電流:30 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VFQFPN-48 封裝:Tray |

| CYP15G0403DXB-BGXI | 功能描述:電信線(xiàn)路管理 IC Ind. Clock Quad HOTLink II Xcvr RoHS:否 制造商:STMicroelectronics 產(chǎn)品:PHY 接口類(lèi)型:UART 電源電壓-最大:18 V 電源電壓-最小:8 V 電源電流:30 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VFQFPN-48 封裝:Tray |

| CYP15G04K100V1 | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:Physical Layer Devices |

| CYP7C1048AC | 制造商:Cypress Semiconductor 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。