- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄379098 > CYD36S72V18 (Cypress Semiconductor Corp.) FullFlex Synchronous SDR Dual-Port SRAM(FullFlex同步SDR雙端口SRAM) PDF資料下載

參數(shù)資料

| 型號(hào): | CYD36S72V18 |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | FullFlex Synchronous SDR Dual-Port SRAM(FullFlex同步SDR雙端口SRAM) |

| 中文描述: | FullFlex器件特別提款權(quán)同步雙端口SRAM(FullFlex器件同步雙端口SRAM的特別提款權(quán)) |

| 文件頁(yè)數(shù): | 2/52頁(yè) |

| 文件大?。?/td> | 774K |

| 代理商: | CYD36S72V18 |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)

FullFlex

Document #: 38-06082 Rev. *F

Page 2 of 52

Notes:

1. The CYD36S18V18 device has 21 address bits. The CYD36S36V18 and the CYD18S18V18 devices have 20 address bits. The CYD36S72V18, CYD18S36V18,

and the CYD09S18V18 devices have 19 address bits. The CYD18S72V18, CYD09S36V18, and the CYD04S18V18 devices have 18 address bits. The

CYD09S72V18 and the CYD04S36V18 devices have 17 address bits. The CYD04S72V18 has 16 address bits.

2. The FullFlex72 family of devices has 72 data lines. The FullFlex36 family of devices has 36 data lines. The FullFlex18 family of devices has 18 data lines.

3. The FullFlex72 family of devices has eight byte enables. The FullFlex36 family of devices has four byte enables. The FullFlex18 family of devices has two byte

enables.

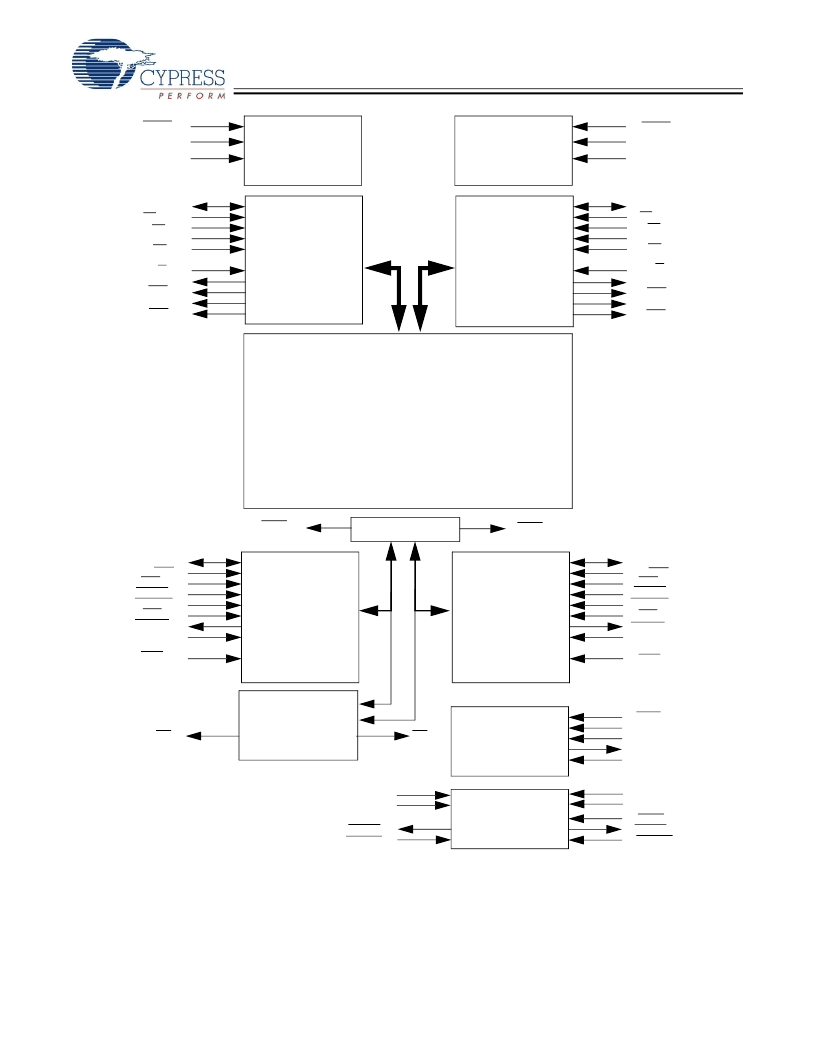

FTSEL

L

CQEN

L

PORTSTD[1:0]

L

DQ[71:0]

L

BE [7:0]

L

CE0

L

CE1

L

OE

L

R/W

L

CQ1

L

FTSEL

R

CQEN

R

PORTSTD[1:0]

R

DQ [71:0]

R

BE [7:0]

R

CE0

R

CE1

R

OE

R

R/W

R

CQ1

R

CQ1

R

CQ0

R

CQ0

R

A [20:0]

L

CNT/MSK

L

ADS

L

CNTEN

L

CNTRST

L

RET

L

CNTINT

L

C

L

WRP

L

A [20:0]

R

CNT/MSK

R

ADS

R

CNTEN

R

CNTRST

R

RET

R

CNTINT

R

C

R

WRP

R

CONFIG Block

CONFIG Block

IO

Control

IO

Control

Address &

Counter Logic

Address &

Counter Logic

INT

L

TRST

TMS

TDI

TDO

TCK

JTAG

MRST

READY

R

LowSPD

R

READY

L

LowSPD

L

RESET

LOGIC

INT

R

BUSY

L

BUSY

R

Mailboxes

Collision Detection Logic

Dual Ported Array

Figure 1. FullFlex72 18-Mbit (CYD18S72V18) Block Diagram

[1, 2, 3]

CQ0

L

CQ0

L

CQ1

L

ZQ0

R

ZQ1

R

ZQ0

L

ZQ1

L

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CYD09S72V18 | FullFlex Synchronous SDR Dual-Port SRAM(FullFlex同步SDR雙端口SRAM) |

| CYD36S18V18 | FullFlex Synchronous SDR Dual-Port SRAM(FullFlex同步SDR雙端口SRAM) |

| CYD36S36V18 | FullFlex Synchronous SDR Dual-Port SRAM(FullFlex同步SDR雙端口SRAM) |

| CYD18S72V | FLEx72 3.3V 64K/128K/256K x 72 Synchronous Dual-Port RAM(FLEx72 3.3V 64K/128K/256K x 72同步雙端口RAM) |

| CYD09S72V | FLEx72 3.3V 64K/128K/256K x 72 Synchronous Dual-Port RAM(FLEx72 3.3V 64K/128K/256K x 72同步雙端口RAM) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CYD36S72V18-167BGXC | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 512K x 72 90nm SDR 36M SYNC DUAL PORT RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CYD36S72V18-167BGXI | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 36MB (512Kx72) 1.8v 167MHz Sync 靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CYD36S72V18-200BGXC | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 36MB (512Kx72) 1.8v 200MHz Sync 靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CYDC064B08 | 制造商:CYPRESS 制造商全稱(chēng):Cypress Semiconductor 功能描述:1.8V 4k/8k/16k x 16 and 8k/16k x 8 ConsuMoBL Dual-Port Static RAM |

| CYDC064B08-40AXC | 制造商:CYPRESS 制造商全稱(chēng):Cypress Semiconductor 功能描述:1.8V 4k/8k/16k x 16 and 8k/16k x 8 ConsuMoBL Dual-Port Static RAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。