- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378513 > CY7C68013A-128AXC (CYPRESS SEMICONDUCTOR CORP) CAC 2C 2#12 PIN PLUG PDF資料下載

參數(shù)資料

| 型號: | CY7C68013A-128AXC |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | CAC 2C 2#12 PIN PLUG |

| 中文描述: | 8-BIT, EEPROM, 48 MHz, MICROCONTROLLER, PQFP128 |

| 封裝: | 14 X 20 MM, 1.40 MM HEIGHT, LEAD FREE, PLASTIC, MS-026, TQFP-128 |

| 文件頁數(shù): | 43/55頁 |

| 文件大小: | 1958K |

| 代理商: | CY7C68013A-128AXC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁當前第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁

CY7C68013A/CY7C68014A

CY7C68015A/CY7C68016A

Document #: 38-08032 Rev. *G

Page 43 of 55

9.9

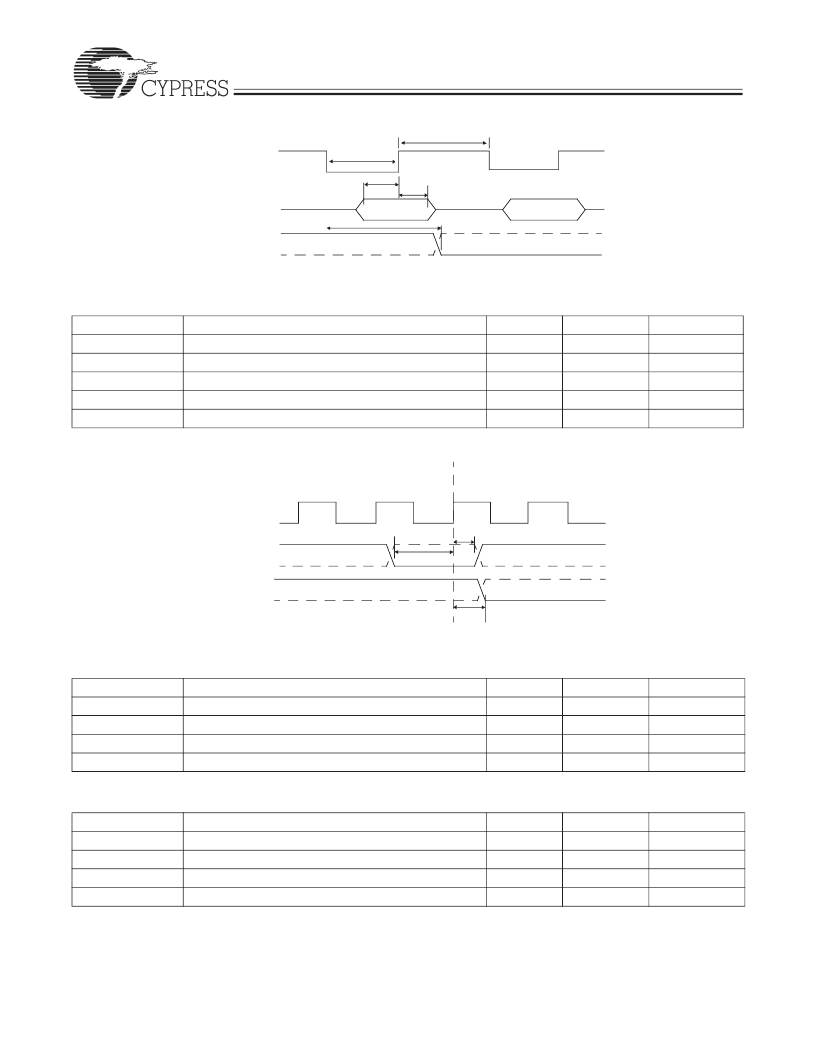

Slave FIFO Asynchronous Write

9.10

Slave FIFO Synchronous Packet End Strobe

There is no specific timing requirement that needs to be met

for asserting PKTEND pin with regards to asserting SLWR.

PKTEND can be asserted with the last data value clocked into

the FIFOs or thereafter. The only consideration is the set-up

time t

SPE

and the hold time t

PEH

must be met.

Although there are no specific timing requirement for the

PKTEND assertion, there is a specific corner case condition

DATA

t

SFD

t

FDH

FLAGS

t

XFD

SLWR/SLCS#

t

WRpwh

t

WRpwl

Figure 9-8. Slave FIFO Asynchronous Write Timing Diagram

[19]

Table 9-11. Slave FIFO Asynchronous Write Parameters with Internally Sourced IFCLK

[23]

Parameter

t

WRpwl

t

WRpwh

t

SFD

t

FDH

t

XFD

Description

Min.

50

70

10

10

Max.

Unit

ns

ns

ns

ns

ns

SLWR Pulse LOW

SLWR Pulse HIGH

SLWR to FIFO DATA Set-up Time

FIFO DATA to SLWR Hold Time

SLWR to FLAGS Output Propagation Delay

70

FLAGS

t

XFLG

IFCLK

PKTEND

t

SPE

t

PEH

Figure 9-9. Slave FIFO Synchronous Packet End Strobe Timing Diagram

[19]

Table 9-12. Slave FIFO Synchronous Packet End Strobe Parameters with Internally Sourced IFCLK

[21]

Parameter

t

IFCLK

t

SPE

t

PEH

t

XFLG

Description

Min.

20.83

14.6

0

Max.

Unit

ns

ns

ns

ns

IFCLK Period

PKTEND to Clock Set-up Time

Clock to PKTEND Hold Time

Clock to FLAGS Output Propagation Delay

9.5

Table 9-13. Slave FIFO Synchronous Packet End Strobe Parameters with Externally Sourced IFCLK

[21]

Parameter

t

IFCLK

t

SPE

t

PEH

t

XFLG

Description

Min.

20.83

8.6

2.5

Max.

200

Unit

ns

ns

ns

ns

IFCLK Period

PKTEND to Clock Set-up Time

Clock to PKTEND Hold Time

Clock to FLAGS Output Propagation Delay

13.5

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C68024 | EZ-USB NX2LP USB 2.0 NAND Flash Controller(EZ-USB NX2LP USB 2.0 NAND閃存控制器) |

| CY7C68023 | EZ-USB NX2LP USB 2.0 NAND Flash Controller(EZ-USB NX2LP USB 2.0 NAND閃存控制器) |

| CY7C9235A | SMPTE-259M/DVB-ASI Scrambler/Controller(SMPTE-259M/DVB-ASI擾頻器/控制器) |

| CY7C924ADX | 200 MBaud HOTLink Transceiver(200MBaud HOTLink收發(fā)器) |

| CY7C924DX | 200-MBaud HOTLink Transceiver(200H波特?zé)峤硬迨瞻l(fā)器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C68013A-128AXCKJ | 制造商:Cypress Semiconductor 功能描述: |

| CY7C68013A-128AXI | 功能描述:8位微控制器 -MCU EZ USB FX2LP LO PWR LO IND RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| CY7C68013A-128AXIKJ | 制造商:Cypress Semiconductor 功能描述: |

| CY7C68013A56BAXC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C68013A-56BAXC | 功能描述:8位微控制器 -MCU EZ USB FX2LP LO PWR LO COM RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。