- 您現(xiàn)在的位置:買賣IC網 > PDF目錄379094 > CY7C43663AV (Cypress Semiconductor Corp.) 3.3V 4K x36 Unidirectional Synchronous FIFO w/ Bus Matching(3.3V 4K x36 單向同步先進先出帶總線匹配) PDF資料下載

參數(shù)資料

| 型號: | CY7C43663AV |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | 3.3V 4K x36 Unidirectional Synchronous FIFO w/ Bus Matching(3.3V 4K x36 單向同步先進先出帶總線匹配) |

| 中文描述: | 3.3 4K的x36單向同步FIFO瓦特/總線匹配(3.3 4K的x36單向同步先進先出帶總線匹配) |

| 文件頁數(shù): | 5/28頁 |

| 文件大?。?/td> | 420K |

| 代理商: | CY7C43663AV |

第1頁第2頁第3頁第4頁當前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

CY7C43643AV

CY7C43663AV/CY7C43683AV

5

PRELIMINARY

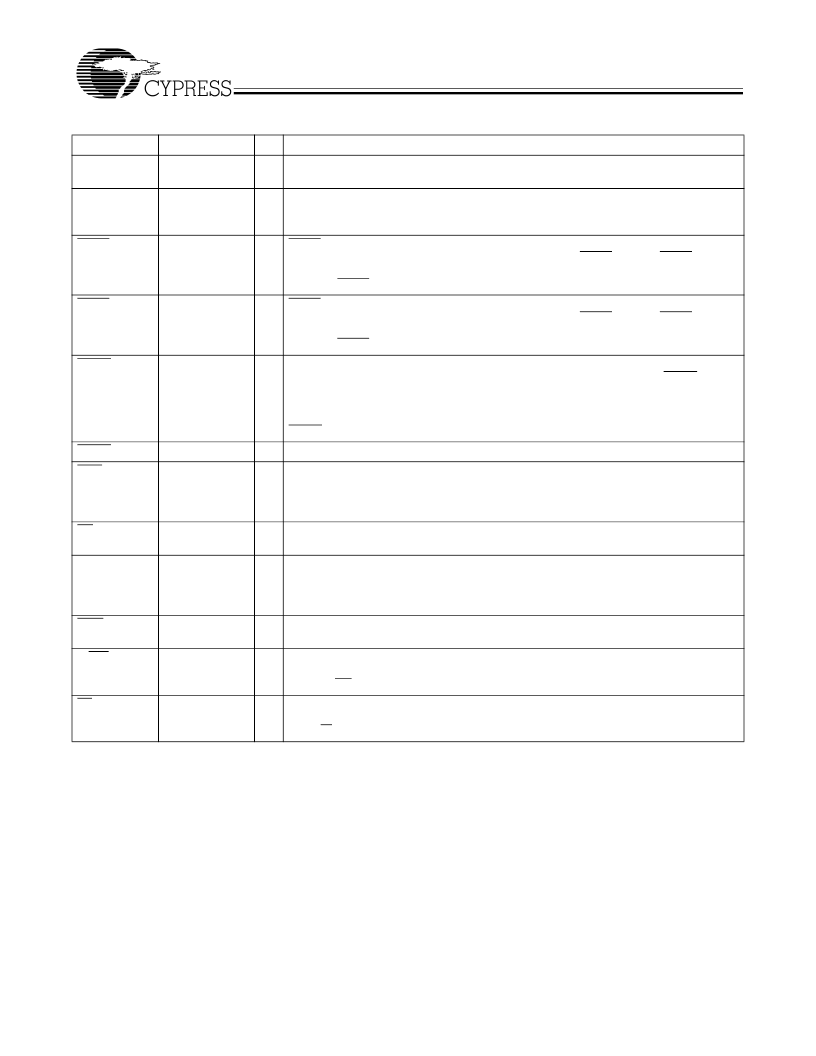

MBA

Port A Mailbox

Select

I

A HIGH level on MBA chooses a mailbox register for a Port A read or write operation.

MBB

Port B Mailbox

Select

I

A HIGH level on MBB chooses a mailbox register for a Port B read or write operation.

When the B

0

–

35

outputs are active, a HIGH level on MBB selects data from the Mail1

register for output and a LOW level selects FIFO output register data for output.

MBF1

Mail1 Register

Flag

O

MBF1 is set LOW by a LOW-to-HIGH transition of CLKA that writes data to the Mail1

register. Writes to the Mail1 register are inhibited while MBF1 is LOW. MBF1 is set

HIGH by a LOW-to-HIGH transition of CLKB when a Port B read is selected and MBB

is HIGH. MBF1 is set HIGH following either a Master or Partial Reset.

MBF2

Mail2 Register

Flag

O

MBF2 is set LOW by a LOW-to-HIGH transition of CLKB that writes data to the Mail2

register. Writes to the Mail2 register are inhibited while MBF2 is LOW. MBF2 is set

HIGH by a LOW-to-HIGH transition of CLKA when a Port A read is selected and MBA

is HIGH. MBF2 is set HIGH following either a Master or Partial Reset.

MRS1

Master Reset

I

A LOW on this pin initializes the FIFO read and write pointers to the first location of

memory and sets the Port B output register to all zeroes. A LOW pulse on MRS1 selects

the programming method (serial or parallel) and one of three programmable flag default

offsets. It also configures Port B for bus size and endian arrangement. Four LOW-to-

HIGH transitions of CLKA and four LOW-to-HIGH transitions of CLKB must occur while

MRS1 is LOW.

MRS2

Master Reset

I

A LOW on this pin initializes the Mail2 Register.

PRS

Partial Reset

I

A LOW on this pin initializes the FIFO read and write pointers to the first location of

memory and sets the Port B output register to all zeroes. During Partial Reset, the

currently selected bus size, endian arrangement, programming method (serial or par-

allel), and programmable flag settings are all retained.

RT

Retransmit

I

A LOW strobe on this pin will retransmit data on FIFO from the location of the write

pointer at the last Partial or Master reset.

SIZE

Bus Size Select

I

A HIGH on this pin when BM is HIGH selects byte bus (9-bit) size on Port B. A LOW

on this pin when BM is HIGH selects word (18-bit) bus size. SIZE works with BM and

BE to select the bus size and endian arrangement for Port B. The level of SIZE must

be static throughout device operation.

SPM

Serial

Programming

I

A LOW on this pin selects serial programming of partial flag offsets. A HIGH on this pin

selects parallel programming or default offsets (8, 16, or 64).

W/RA

Port A Write/

Read Select

I

A HIGH selects a write operation and a LOW selects a read operation on Port A for a

LOW-to-HIGH transition of CLKA. The A

0

–

35

outputs are in the high-impedance state

when W/RA is HIGH.

W/RB

Port B Write/

Read Select

I

A LOW selects a write operation and a HIGH selects a read operation on Port B for a

LOW-to-HIGH transition of CLKB. The B

0

–

35

outputs are in the high-impedance state

when W/RB is LOW.

Pin Definitions

(continued)

Signal Name

Description

I/O

Function

相關PDF資料 |

PDF描述 |

|---|---|

| CY7C43683AV | 3.3V 16K x36 Unidirectional Synchronous FIFO w/ Bus Matching(3.3V 16K x36 單向同步先進先出帶總線匹配) |

| CY7C43664AV | 3.3V 4K x36 x2 Bidirectional Synchronous FIFO w/ Bus Matching(3.3V 4K x36 x2 雙向同步先進先出帶總線匹配) |

| CY7C43644AV | 3.3V 1Kx36 x2 Bidirectional Synchronous FIFO w/ Bus Matching(3.3V 1K x36 x2 雙向同步先進先出帶總線匹配) |

| CY7C43684AV | 3.3V 16K x36 x2 Bidirectional Synchronous FIFO w/ Bus Matching(3.3V 16K x36 x2 雙向同步先進先出帶總線匹配) |

| CY7C43666AV | 3.3V 4K x36/x18x2 Tri Bus FIFO(3.3V 4K x36/x18x2 三路總線先進先出) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C43664-7AC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY7C43682-15AC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY7C43683-10AI | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY7C43683AV-15AC | 制造商:Cypress Semiconductor 功能描述:FIFO Mem Sync Dual Depth/Width Uni-Dir 16K x 36 128-Pin TQFP 制造商:Rochester Electronics LLC 功能描述:3.3V SYNC FIFO W/BUS MATCHING 16K X36 (NOT IDT COMPAT) - Bulk |

| CY7C43684-10AC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。