- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379092 > CY7C4215 (Cypress Semiconductor Corp.) 512 x 18 Synchronous FIFOs(512 x 18 同步 先進先出) PDF資料下載

參數(shù)資料

| 型號: | CY7C4215 |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | 512 x 18 Synchronous FIFOs(512 x 18 同步 先進先出) |

| 中文描述: | 512 × 18(512 × 18同步先進先出同步FIFO的) |

| 文件頁數(shù): | 16/25頁 |

| 文件大小: | 398K |

| 代理商: | CY7C4215 |

CY7C4425/4205/4215

CY7C4225/4235/4245

16

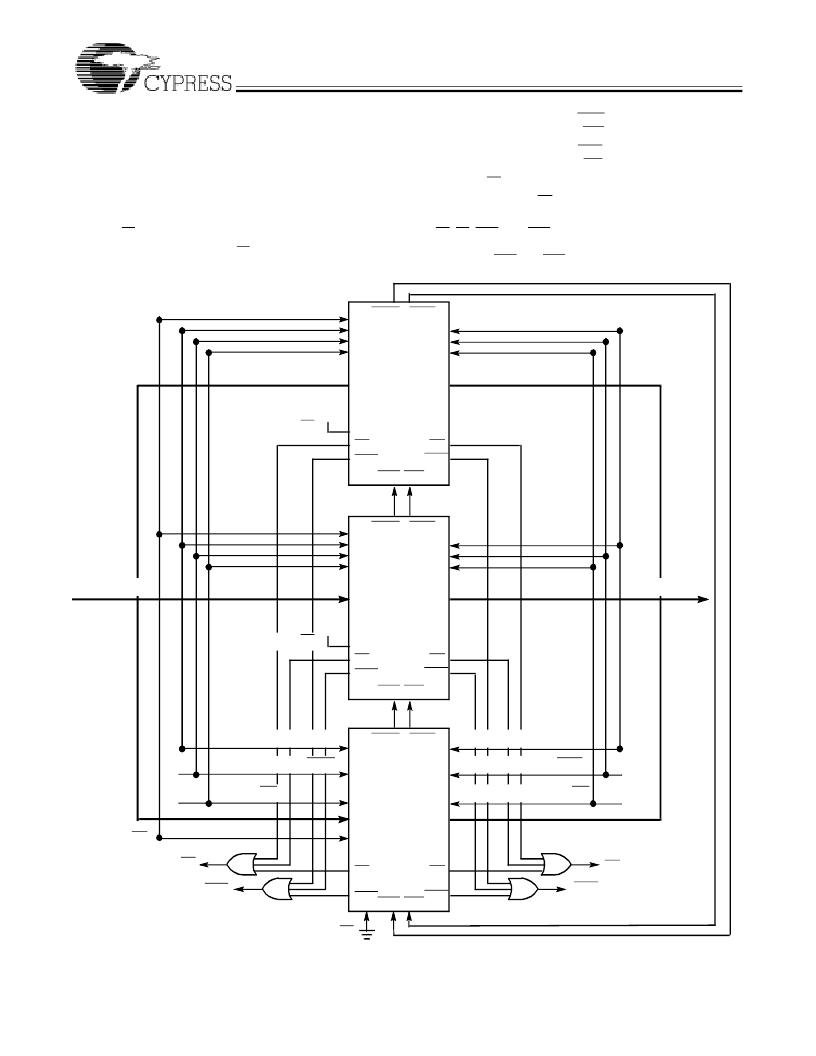

Depth Expansion Configuration

(with Programmable Flags)

The CY7C42X5 can easily be adapted to applications requir-

ing more than 64/256/512/1024/2048/4096 words of buffering.

Figure2 shows Depth Expansion using three CY7C42X5s. Maxi-

mum depth is limited only by signal loading. Follow these steps:

1. The first device must be designated by grounding the First

Load (FL) control input.

2. All other devices must have FL in the HIGH state.

3. The Write Expansion Out (WXO) pin of each device must be

tied to the Write Expansion In (WXI) pin of the next device.

4. The Read Expansion Out (RXO) pin of each device must be

tied to the Read Expansion In (RXI) pin of the next device.

5. All Load (LD) pins are tied together.

6. The Half-Full Flag (HF) is not available in the Depth Expansion

Configuration.

7. EF, FF, PAE, and PAF are created with composite flags by

ORing together these respective flags for monitoring. The

composite PAE and PAF flags are not precise.

Figure 2. Block Diagram of 192 x 18/768 x 18/1536 x 18/3072 x 18/12288 x 18 Synchronous FIFO Memory

with Programmable Flags used in Depth Expansion Configuration

42X5–23

WRITECLOCK(WCLK)

WRITE ENABLE(WEN)

RESET(RS)

LOAD(LD)

FF

PAF

PAF

FF

EF

PAE

PAE

EF

WXI RXI

FIRSTLOAD(FL)

READCLOCK(RCLK)

READ ENABLE (REN)

OUTPUT ENABLE(OE)

WXO RXO

7C4425

7C4205

7C4215

7C4225

7C4235

7C4235

PAF

FF

EF

PAE

WXI RXI

WXO RXO

7C4425

7C4205

7C4215

7C4225

7C4235

7C4235

V

CC

FIRSTLOAD(FL)

PAF

FF

EF

PAE

WXI RXI

WXO RXO

7C4425

7C4205

7C4215

7C4225

7C4235

7C4235

V

CC

FIRSTLOAD(FL)

DATAIN (D)

DATAOUT(Q)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C4235 | 2K x 18 Synchronous FIFOs(2K x 18 同步先進先出) |

| CY7C4425 | 64 x 18 Synchronous FIFOs(64 x 18 同步 先進先出) |

| CY7C4211 | 512 x 9 Synchronous FIFOs(512x9同步先進先出(FIFO)) |

| CY7C4201 | 256 x 9 Synchronous FIFOs(256x9同步先進先出(FIFO)) |

| CY7C4221 | 1K x 9 Synchronous FIFOs(1Kx9同步先進先出(FIFO)) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C4215 WAF | 制造商:Cypress Semiconductor 功能描述: |

| CY7C4215-15AI | 制造商:Cypress Semiconductor 功能描述: |

| CY7C4215-15AIT | 制造商:Cypress Semiconductor 功能描述: |

| CY7C4215-15AXI | 功能描述:先進先出 512x18 IDT Compat SYNC 先進先出 IND RoHS:否 制造商:IDT 電路數(shù)量: 數(shù)據(jù)總線寬度:18 bit 總線定向:Unidirectional 存儲容量:4 Mbit 定時類型:Synchronous 組織:256 K x 18 最大時鐘頻率:100 MHz 訪問時間:10 ns 電源電壓-最大:3.6 V 電源電壓-最小:6 V 最大工作電流:35 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-80 封裝: |

| CY7C4215-15AXIT | 功能描述:先進先出 512x18 IDT Compat SYNC 先進先出 IND RoHS:否 制造商:IDT 電路數(shù)量: 數(shù)據(jù)總線寬度:18 bit 總線定向:Unidirectional 存儲容量:4 Mbit 定時類型:Synchronous 組織:256 K x 18 最大時鐘頻率:100 MHz 訪問時間:10 ns 電源電壓-最大:3.6 V 電源電壓-最小:6 V 最大工作電流:35 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-80 封裝: |

發(fā)布緊急采購,3分鐘左右您將得到回復。