- 您現(xiàn)在的位置:買賣IC網 > PDF目錄379092 > CY7C4215 (Cypress Semiconductor Corp.) 512 x 18 Synchronous FIFOs(512 x 18 同步 先進先出) PDF資料下載

參數資料

| 型號: | CY7C4215 |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | 512 x 18 Synchronous FIFOs(512 x 18 同步 先進先出) |

| 中文描述: | 512 × 18(512 × 18同步先進先出同步FIFO的) |

| 文件頁數: | 10/25頁 |

| 文件大小: | 398K |

| 代理商: | CY7C4215 |

CY7C4425/4205/4215

CY7C4225/4235/4245

10

Notes:

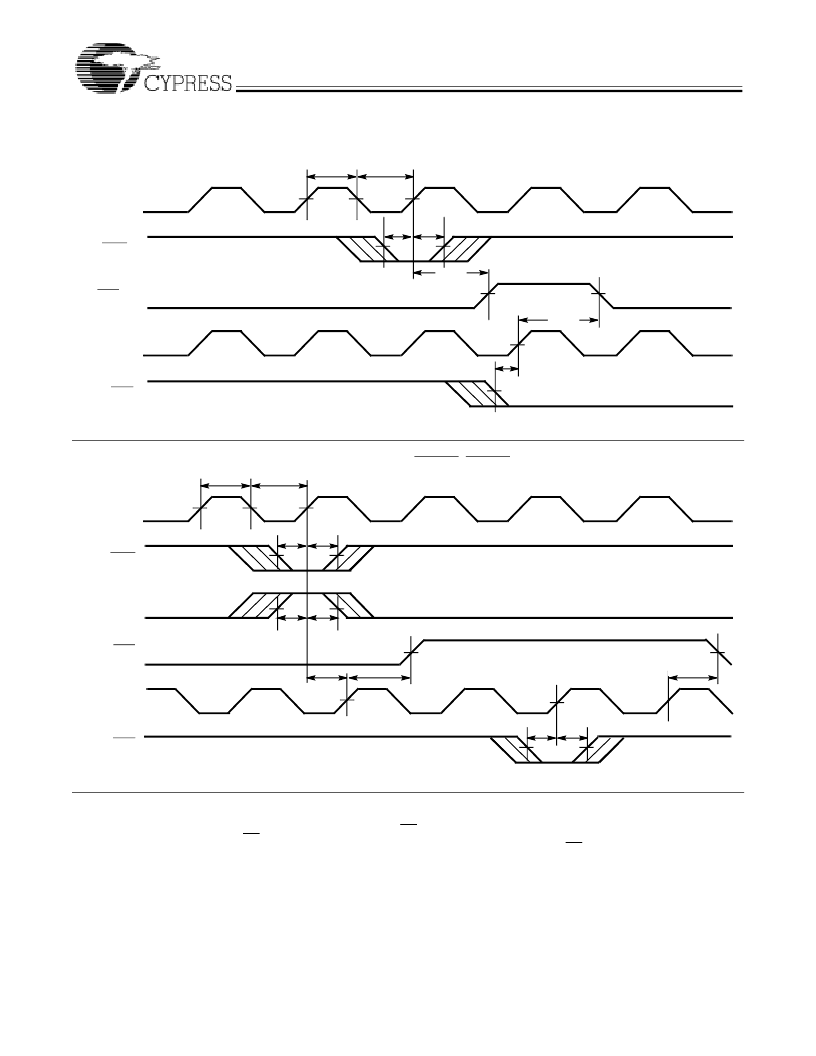

19. PAE offset – n. Number of data words into FIFO already = n.

20. PAE offset – n.

21. t

is the minimum time between a rising WCLK and a rising RCLK edge for PAE to change state during that clock cycle. If the time between the edge of WCLK and the

rising RCLK is less than t

, then PAE may not change state until the next RCLK.

22. If a read is performed on this rising edge of the read clock, there will be Empty + (n – 1) words in the FIFO when PAE goes LOW.

Switching Waveforms

(continued)

t

ENH

Programmable Almost EmptyFlagTiming

WCLK

PAE

]

REN

RCLK

t

CLKH

t

PAE

t

ENS

n+1

WORDS

IN FIFO

t

CLKL

t

ENS

t

PAE

n WORDS IN FIFO

42X5–13

[19]

WEN

Note

20

t

ENH

WCLK

PAE

RCLK

t

CLKH

t

ENS

t

CLKL

t

ENS

t

PAEsynch

N + 1 WORDS

INFIFO

42X5–14

t

ENH

t

ENS

t

ENH

t

ENS

t

PAEsynch

REN

WEN

WEN2

t

SKEW3

Note

22

Programmable Almost Empty Flag Timing (applies only in SMODE (SMODE is LOW)

[21]

相關PDF資料 |

PDF描述 |

|---|---|

| CY7C4235 | 2K x 18 Synchronous FIFOs(2K x 18 同步先進先出) |

| CY7C4425 | 64 x 18 Synchronous FIFOs(64 x 18 同步 先進先出) |

| CY7C4211 | 512 x 9 Synchronous FIFOs(512x9同步先進先出(FIFO)) |

| CY7C4201 | 256 x 9 Synchronous FIFOs(256x9同步先進先出(FIFO)) |

| CY7C4221 | 1K x 9 Synchronous FIFOs(1Kx9同步先進先出(FIFO)) |

相關代理商/技術參數 |

參數描述 |

|---|---|

| CY7C4215 WAF | 制造商:Cypress Semiconductor 功能描述: |

| CY7C4215-15AI | 制造商:Cypress Semiconductor 功能描述: |

| CY7C4215-15AIT | 制造商:Cypress Semiconductor 功能描述: |

| CY7C4215-15AXI | 功能描述:先進先出 512x18 IDT Compat SYNC 先進先出 IND RoHS:否 制造商:IDT 電路數量: 數據總線寬度:18 bit 總線定向:Unidirectional 存儲容量:4 Mbit 定時類型:Synchronous 組織:256 K x 18 最大時鐘頻率:100 MHz 訪問時間:10 ns 電源電壓-最大:3.6 V 電源電壓-最小:6 V 最大工作電流:35 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-80 封裝: |

| CY7C4215-15AXIT | 功能描述:先進先出 512x18 IDT Compat SYNC 先進先出 IND RoHS:否 制造商:IDT 電路數量: 數據總線寬度:18 bit 總線定向:Unidirectional 存儲容量:4 Mbit 定時類型:Synchronous 組織:256 K x 18 最大時鐘頻率:100 MHz 訪問時間:10 ns 電源電壓-最大:3.6 V 電源電壓-最小:6 V 最大工作電流:35 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-80 封裝: |

發(fā)布緊急采購,3分鐘左右您將得到回復。