- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379087 > CY7C1522AV18-250BZI (CYPRESS SEMICONDUCTOR CORP) 72-Mbit DDR-II SIO SRAM 2-Word Burst Architecture PDF資料下載

參數(shù)資料

| 型號(hào): | CY7C1522AV18-250BZI |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | DRAM |

| 英文描述: | 72-Mbit DDR-II SIO SRAM 2-Word Burst Architecture |

| 中文描述: | 8M X 8 DDR SRAM, 0.45 ns, PBGA165 |

| 封裝: | 15 X 17 MM, 1.40 MM HEIGHT, MO-216, FBGA-165 |

| 文件頁(yè)數(shù): | 19/28頁(yè) |

| 文件大小: | 1133K |

| 代理商: | CY7C1522AV18-250BZI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)當(dāng)前第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)

PRELIMINARY

CY7C1522AV18

CY7C1529AV18

CY7C1523AV18

CY7C1524AV18

Document #: 001-06981 Rev. *B

Page 19 of 28

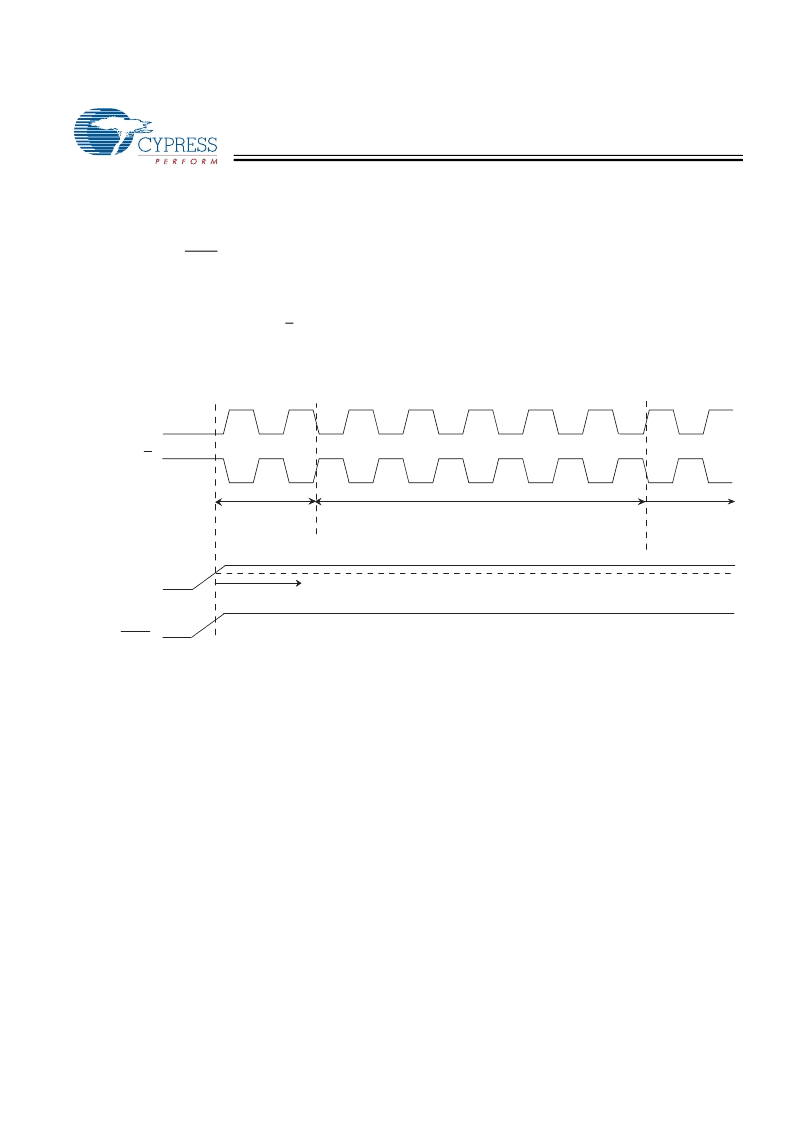

Power-Up Sequence in DDR-II SRAM

[14]

DDR-II SRAMs must be powered up and initialized in a

predefined manner to prevent undefined operations.

Power-Up Sequence

Apply power with DOFF tied HIGH (All other inputs can be

HIGH or LOW)

— Apply V

DD

before V

DDQ

— Apply V

DDQ

before V

REF

or at the same time as V

REF

Provide stable power and clock (K, K) for 1024 cycles to

lock the DLL.

DLL Constraints

DLL uses K clock as its synchronizing input. The input

should have low phase jitter, which is specified as t

KC Var

.

The DLL will function at frequencies down to 80 MHz.

If the input clock is unstable and the DLL is enabled, then

the DLL may lock onto an incorrect frequency, causing

unstable SRAM behavior. To avoid this, provide 1024 cycles

stable clock to relock to the desired clock frequency.

Power-Up Waveforms

Note:

14.During Power-Up, when the DOFF is tied HIGH, the DLL gets locked after 1024 cycles of stable clock.

> 1024 Stable clock

Start Normal

Operation

DOFF

Stabl

e

(< +/- 0.1V DC per 50ns )

Fix High (or tied to VDDQ)

K

K

DDQ

V

DD

V

/

DDQ

DD

V

V

/

Clock Start

(

Clock Starts after DD

)

V

/

~

~

~

~

Unstable Clock

[+] Feedback

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C1522AV18-250BZXC | 72-Mbit DDR-II SIO SRAM 2-Word Burst Architecture |

| CY7C1522AV18-250BZXI | 72-Mbit DDR-II SIO SRAM 2-Word Burst Architecture |

| CY7C1523AV18-300BZC | 72-Mbit DDR-II SIO SRAM 2-Word Burst Architecture |

| CY7C1523AV18-300BZI | 72-Mbit DDR-II SIO SRAM 2-Word Burst Architecture |

| CY7C1523AV18-300BZXC | 72-Mbit DDR-II SIO SRAM 2-Word Burst Architecture |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1523AV18-200BZC | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 4M x 18 1.8V DDR II SIO 靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1523AV18-250BZC | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 4M x 18 1.8V DDR II SIO 靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1523JV18-300BZXC | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 4Mbx18 72Mb 1.7-1.9V 300 MHz 2 WORD BURST RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1523KV18-250BZ | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1523KV18-250BZXC | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 72MB (4Mx18) 1.8v 250MHz DDR II 靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。