- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379077 > CY7C1475V25-133BGXI (CYPRESS SEMICONDUCTOR CORP) 72-Mbit (2M x 36/4M x 18/1M x 72) Flow-Through SRAM with NoBL⑩ Architecture PDF資料下載

參數(shù)資料

| 型號(hào): | CY7C1475V25-133BGXI |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | DRAM |

| 英文描述: | 72-Mbit (2M x 36/4M x 18/1M x 72) Flow-Through SRAM with NoBL⑩ Architecture |

| 中文描述: | 1M X 72 ZBT SRAM, 6.5 ns, PBGA209 |

| 封裝: | 14 X 22 MM, 1.76 MM HEIGHT, LEAD FREE, FBGA-209 |

| 文件頁數(shù): | 18/32頁 |

| 文件大小: | 928K |

| 代理商: | CY7C1475V25-133BGXI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當(dāng)前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

CY7C1471V25

CY7C1473V25

CY7C1475V25

Document #: 38-05287 Rev. *I

Page 18 of 32

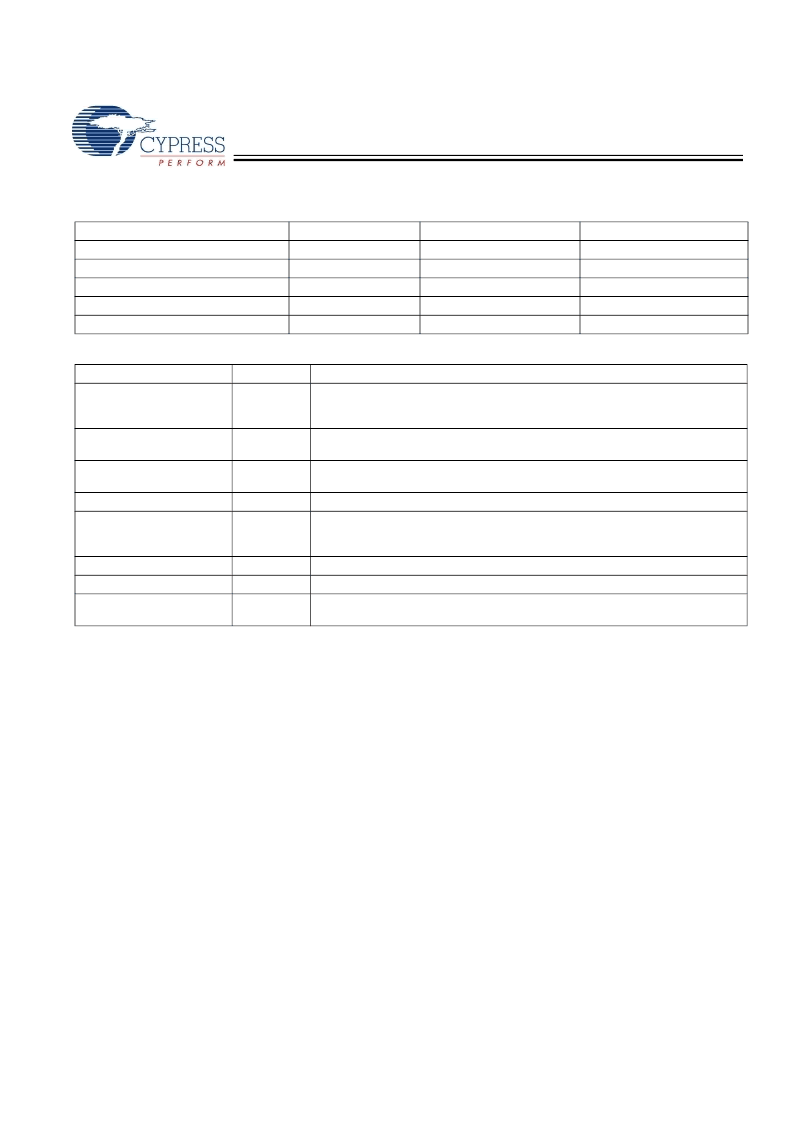

Scan Register Sizes

Register Name

Bit Size (x36)

3

1

32

71

-

Bit Size (x18)

3

1

32

52

-

Bit Size (x72)

3

1

32

-

110

Instruction

Bypass

ID

Boundary Scan Order – 165FBGA

Boundary Scan Order – 209BGA

Identification Codes

Instruction

Code

000

Description

EXTEST

Captures IO ring contents. Places the boundary scan register between TDI and

TDO. Forces all SRAM outputs to High-Z state. This instruction is not 1149.1

compliant.

Loads the ID register with the vendor ID code and places the register between TDI

and TDO. This operation does not affect SRAM operations.

Captures IO ring contents. Places the boundary scan register between TDI and

TDO. Forces all SRAM output drivers to a High-Z state.

Do Not Use: This instruction is reserved for future use.

Captures IO ring contents. Places the boundary scan register between TDI and

TDO. Does not affect SRAM operation. This instruction does not implement 1149.1

preload function and is therefore not 1149.1 compliant.

Do Not Use: This instruction is reserved for future use.

Do Not Use: This instruction is reserved for future use.

Places the bypass register between TDI and TDO. This operation does not affect

SRAM operation.

IDCODE

001

SAMPLE Z

010

RESERVED

SAMPLE/PRELOAD

011

100

RESERVED

RESERVED

BYPASS

101

110

111

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C1475V25 | 72-Mbit (2M x 36/4M x 18/1M x 72) Flow-Through SRAM with NoBL Architecture(帶NoBL結(jié)構(gòu)的72-Mbit (2M x 36/4M x 18/1M x 72) Flow-Through SRAM) |

| CY7C1473V25 | 72-Mbit (2M x 36/4M x 18/1M x 72) Flow-Through SRAM with NoBL Architecture(帶NoBL結(jié)構(gòu)的72-Mbit (2M x 36/4M x 18/1M x 72) Flow-Through SRAM) |

| CY7C1475V33 | 72-Mbit (2M x 36/4M x 18/1M x 72) Flow-Through SRAM with NoBL Architecture(帶NoBL結(jié)構(gòu)的72-Mbit (2M x 36/4M x 18/1M x 72) Flow-Through SRAM) |

| CY7C1471V33 | 72-Mbit (2M x 36/4M x 18/1M x 72) Flow-Through SRAM with NoBL Architecture(帶NoBL結(jié)構(gòu)的72-Mbit (2M x 36/4M x 18/1M x 72) Flow-Through SRAM) |

| CY7C1482V25-200BZXC | 72-Mbit (2M x 36/4M x 18/1M x 72) Pipelined Sync SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1475V33-100AXC | 制造商:Cypress Semiconductor 功能描述:72MB (1MBX72) NOBL FLOW-THRU, 3.3V CORE, 2.5/3.3V I/O - Bulk |

| CY7C1475V33-100BGC | 制造商:Cypress Semiconductor 功能描述:SRAM SYNC SGL 3.3V 72MBIT 1MX72 8.5NS 209FBGA - Bulk |

| CY7C1475V33-133BGC | 制造商:Cypress Semiconductor 功能描述:SRAM SYNC OCTAL 3.3V 72MBIT 1MX72 6.5NS 209FBGA - Bulk |

| CY7C14802BC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C14802XC | 制造商:Cypress Semiconductor 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。