- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379077 > CY7C1475V25-100BGI (CYPRESS SEMICONDUCTOR CORP) 72-Mbit (2M x 36/4M x 18/1M x 72) Flow-Through SRAM with NoBL⑩ Architecture PDF資料下載

參數(shù)資料

| 型號: | CY7C1475V25-100BGI |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | DRAM |

| 英文描述: | 72-Mbit (2M x 36/4M x 18/1M x 72) Flow-Through SRAM with NoBL⑩ Architecture |

| 中文描述: | 1M X 72 ZBT SRAM, 8.5 ns, PBGA209 |

| 封裝: | 14 X 22 MM, 1.76 MM HEIGHT, FBGA-209 |

| 文件頁數(shù): | 26/32頁 |

| 文件大?。?/td> | 928K |

| 代理商: | CY7C1475V25-100BGI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁第28頁第29頁第30頁第31頁第32頁

CY7C1471V25

CY7C1473V25

CY7C1475V25

Document #: 38-05287 Rev. *I

Page 26 of 32

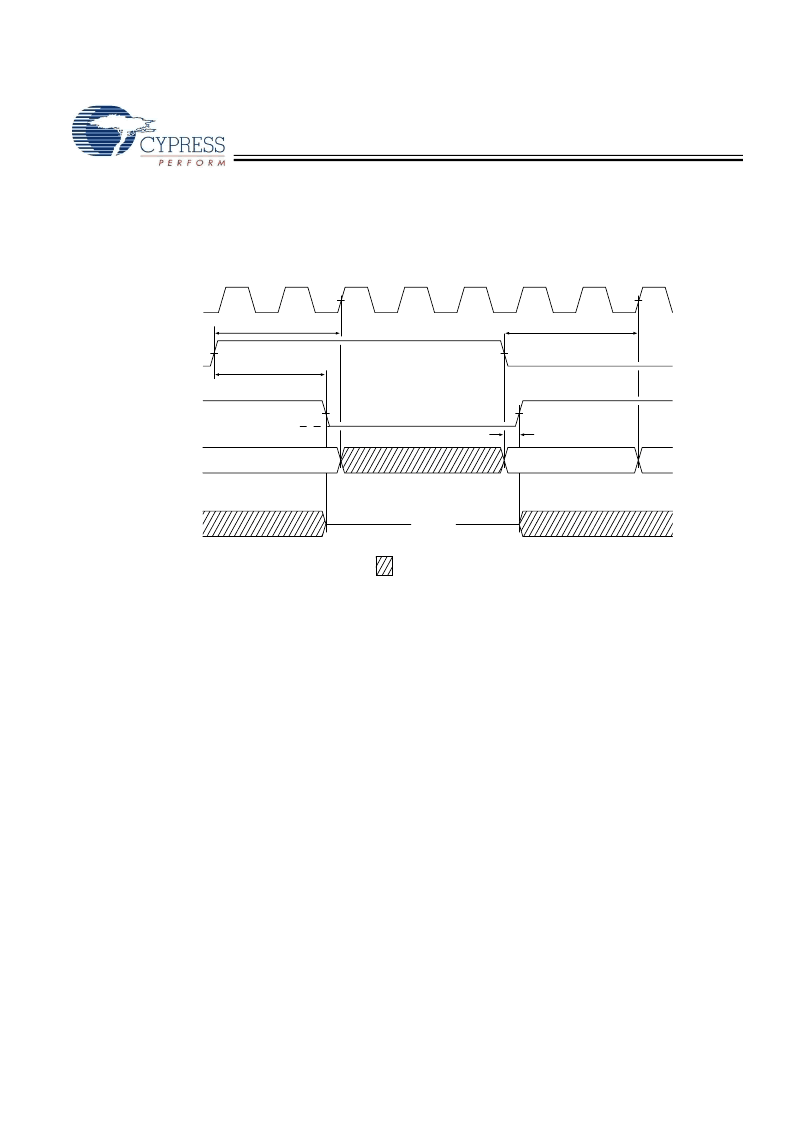

Figure 3

shows ZZ Mode timing waveform.

[23, 24]

Figure 3. ZZ

Mode Timing

Switching Waveforms

(continued)

tZZ

I

SUPPLY

CLK

ZZ

tZZREC

ALL INPUTS

(except ZZ)

DON’T CARE

IDDZZ

tZZI

tRZZI

Outputs (Q)

High-Z

DESELECT or READ Only

Notes

23.Device must be deselected when entering ZZ mode. See

“Truth Table” on page 11

for all possible signal conditions to deselect the device.

24.DQs are in high-Z when exiting ZZ sleep mode.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C1475V25-100BGXI | 72-Mbit (2M x 36/4M x 18/1M x 72) Flow-Through SRAM with NoBL⑩ Architecture |

| CY7C1475V25-133BGI | 72-Mbit (2M x 36/4M x 18/1M x 72) Flow-Through SRAM with NoBL⑩ Architecture |

| CY7C1475V25-133BGXI | 72-Mbit (2M x 36/4M x 18/1M x 72) Flow-Through SRAM with NoBL⑩ Architecture |

| CY7C1475V25 | 72-Mbit (2M x 36/4M x 18/1M x 72) Flow-Through SRAM with NoBL Architecture(帶NoBL結(jié)構(gòu)的72-Mbit (2M x 36/4M x 18/1M x 72) Flow-Through SRAM) |

| CY7C1473V25 | 72-Mbit (2M x 36/4M x 18/1M x 72) Flow-Through SRAM with NoBL Architecture(帶NoBL結(jié)構(gòu)的72-Mbit (2M x 36/4M x 18/1M x 72) Flow-Through SRAM) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1475V33-100AXC | 制造商:Cypress Semiconductor 功能描述:72MB (1MBX72) NOBL FLOW-THRU, 3.3V CORE, 2.5/3.3V I/O - Bulk |

| CY7C1475V33-100BGC | 制造商:Cypress Semiconductor 功能描述:SRAM SYNC SGL 3.3V 72MBIT 1MX72 8.5NS 209FBGA - Bulk |

| CY7C1475V33-133BGC | 制造商:Cypress Semiconductor 功能描述:SRAM SYNC OCTAL 3.3V 72MBIT 1MX72 6.5NS 209FBGA - Bulk |

| CY7C14802BC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C14802XC | 制造商:Cypress Semiconductor 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。