- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄379075 > CY7C1472V33-200BZXC (CYPRESS SEMICONDUCTOR CORP) 72-Mbit (2M x 36/4M x 18/1M x 72) Pipelined SRAM with NoBL Architecture PDF資料下載

參數(shù)資料

| 型號(hào): | CY7C1472V33-200BZXC |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類(lèi): | DRAM |

| 英文描述: | 72-Mbit (2M x 36/4M x 18/1M x 72) Pipelined SRAM with NoBL Architecture |

| 中文描述: | 4M X 18 ZBT SRAM, 3 ns, PBGA165 |

| 封裝: | 15 X 17 MM, 1.40 MM HEIGHT, LEAD FREE, FBGA-165 |

| 文件頁(yè)數(shù): | 13/28頁(yè) |

| 文件大小: | 378K |

| 代理商: | CY7C1472V33-200BZXC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)

PRELIMINARY

CY7C1470V33

CY7C1472V33

CY7C1474V33

Document #: 38-05289 Rev. *E

Page 13 of 28

possible to capture all other signals and simply ignore the

value of the CLK captured in the boundary scan register.

Once the data is captured, it is possible to shift out the data by

putting the TAP into the Shift-DR state. This places the

boundary scan register between the TDI and TDO balls.

Note that since the PRELOAD part of the command is not

implemented, putting the TAP to the Update-DR state while

performing a SAMPLE/PRELOAD instruction will have the

same effect as the Pause-DR command.

BYPASS

When the BYPASS instruction is loaded in the instruction

register and the TAP is placed in a Shift-DR state, the bypass

register is placed between the TDI and TDO balls. The

advantage of the BYPASS instruction is that it shortens the

boundary scan path when multiple devices are connected

together on a board.

Reserved

These instructions are not implemented but are reserved for

future use. Do not use these instructions.

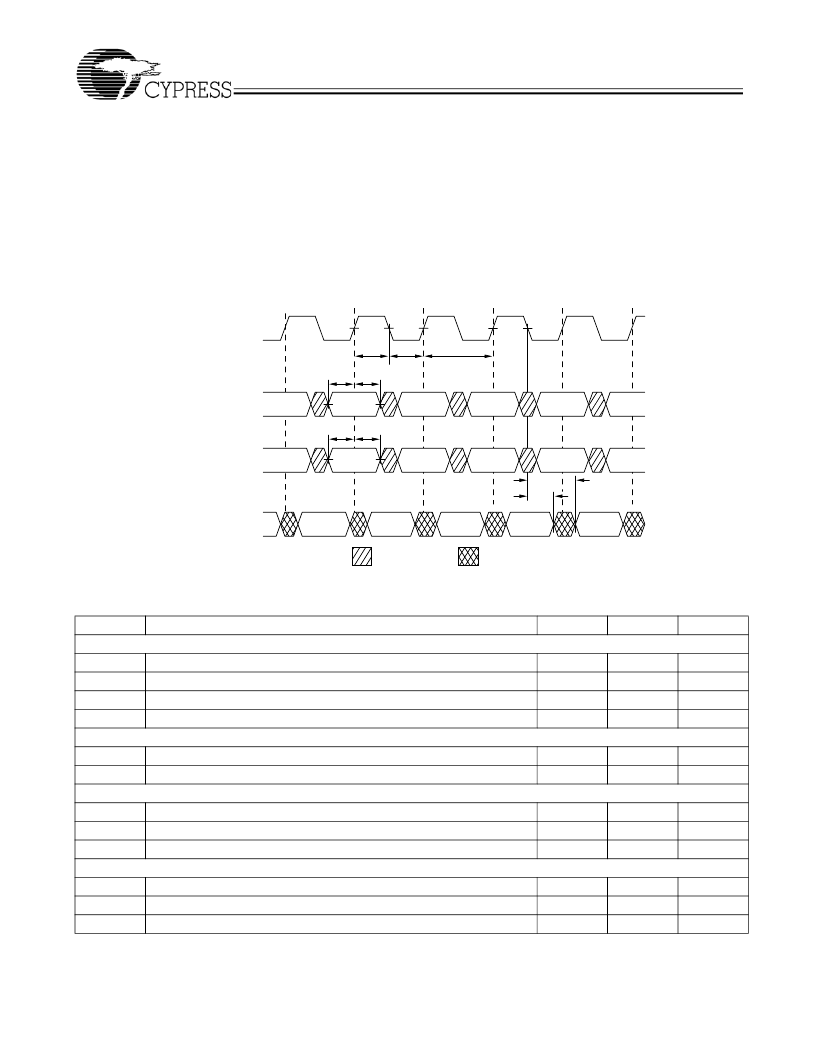

TAP Timing

tTL

Test Clock

(TCK)

1

2

3

4

5

6

Test Mode Select

(TMS)

tTH

Test Data-Out

(TDO)

tCYC

Test Data-In

(TDI)

tTMSH

tTMSS

tTDIH

tTDIS

tTDOX

tTDOV

DON’T CARE

UNDEFINED

TAP AC Switching Characteristics

Over the Operating Range

[9, 10]

Parameter

Clock

t

TCYC

t

TF

t

TH

t

TL

Output Times

t

TDOV

t

TDOX

Set-up Times

t

TMSS

t

TDIS

t

CS

Hold Times

t

TMSH

t

TDIH

t

CH

Notes:

9.

tCS

and t

refer to the set-up and hold time requirements of latching data from the boundary scan register.

10.Test conditions are specified using the load in TAP AC Test Conditions. t

R

/t

F

= 1 ns.

Description

Min.

Max

Unit

TCK Clock Cycle Time

TCK Clock Frequency

TCK Clock HIGH time

TCK Clock LOW time

50

ns

MHz

ns

ns

20

25

25

TCK Clock LOW to TDO Valid

TCK Clock LOW to TDO Invalid

5

ns

ns

0

TMS Set-up to TCK Clock Rise

TDI Set-up to TCK Clock Rise

Capture Set-up to TCK Rise

5

5

5

ns

ns

ns

TMS Hold after TCK Clock Rise

TDI Hold after Clock Rise

Capture Hold after Clock Rise

5

5

5

ns

ns

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C1472V33-250AXC | 72-Mbit (2M x 36/4M x 18/1M x 72) Pipelined SRAM with NoBL Architecture |

| CY7C1472V33-250BZC | 72-Mbit (2M x 36/4M x 18/1M x 72) Pipelined SRAM with NoBL Architecture |

| CY7C1472V33-250BZXC | 72-Mbit (2M x 36/4M x 18/1M x 72) Pipelined SRAM with NoBL Architecture |

| CY7C1474V33 | 72-Mbit (2M x 36/4M x 18/1M x 72) Pipelined SRAM with NoBL Architecture |

| CY7C1474V33-167BGC | 72-Mbit (2M x 36/4M x 18/1M x 72) Pipelined SRAM with NoBL Architecture |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1472V33-250AXC | 制造商:Cypress Semiconductor 功能描述:SRAM SYNC DUAL 3.3V 72MBIT 4MX18 3NS 100TQFP - Bulk |

| CY7C1472XC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C147-35KMB | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1473BV33-133AXC | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 72MB (4Mx18) 3.3v 133MHz 靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1474BV25-167BGC | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 1Mx72, 2.5V NoBL PL RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。