- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379067 > CY7C1372C-167AI (CYPRESS SEMICONDUCTOR CORP) 512K x 36/1M x 18 Pipelined SRAM with NoBL Architecture PDF資料下載

參數(shù)資料

| 型號: | CY7C1372C-167AI |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | DRAM |

| 英文描述: | 512K x 36/1M x 18 Pipelined SRAM with NoBL Architecture |

| 中文描述: | 1M X 18 ZBT SRAM, 3.4 ns, PQFP100 |

| 封裝: | 14 X 20 MM, 1.40 MM HEIGHT, PLASTIC, TQFP-100 |

| 文件頁數(shù): | 16/27頁 |

| 文件大?。?/td> | 704K |

| 代理商: | CY7C1372C-167AI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁

CY7C1370C

CY7C1372C

Document #: 38-05233 Rev. *D

Page 16 of 27

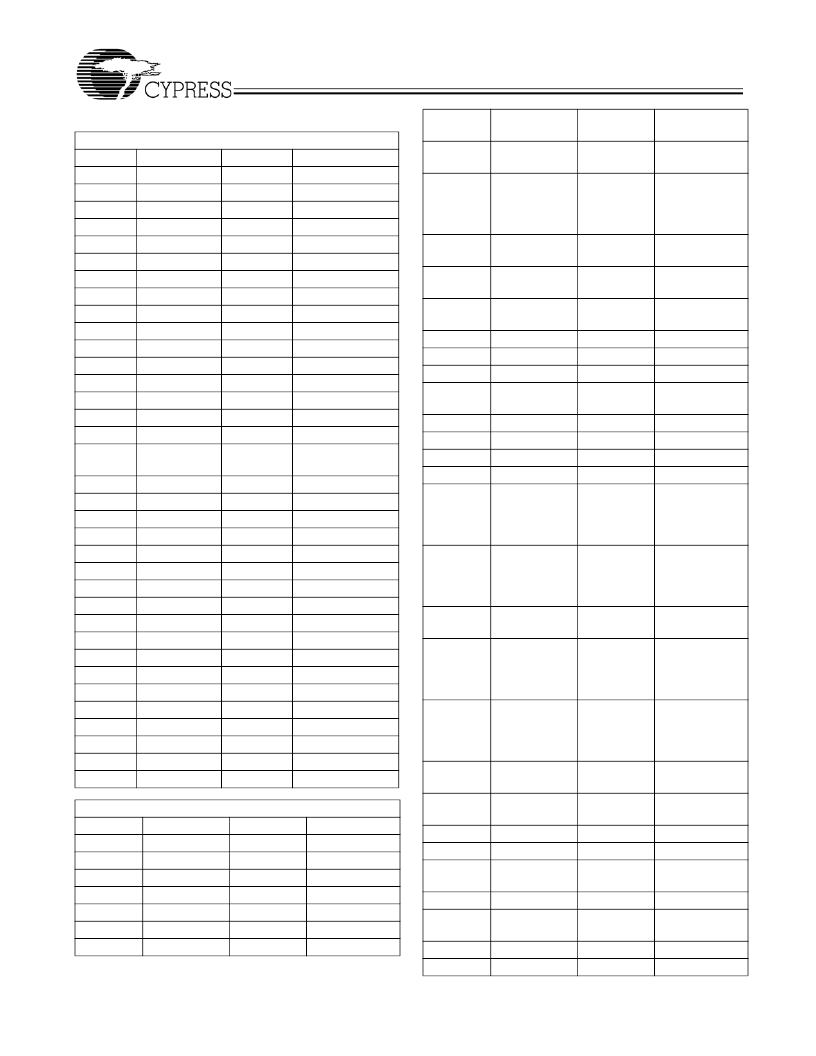

119-ball BGA Boundary Scan Orde

r

CY7C1370C (512K x 36)

Ball ID

K4

H4

M4

F4

B4

A4

G4

C6

A6

D6

D7

E6

G6

H7

E7

F6

G7

Bit#

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

Bit#

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

Ball ID

P4

N4

R6

T5

T3

R2

R3

P2

P1

N2

L2

K1

N1

M2

L1

K2

Not Bonded

(Preset to 1)

H1

G2

E2

D1

H2

G1

F2

E1

D2

A5

A3

E4

B2

L3

G3

G5

L5

B6

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

H6

T7

K7

L6

N6

P7

K6

L7

M6

N7

P6

B5

B3

C5

C3

C2

A2

T4

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

CY7C1372C (1M x 18)

Ball ID

K4

H4

M4

F4

B4

A4

G4

Bit#

1

2

3

4

5

6

7

Bit#

37

38

39

40

36

41

42

Ball ID

N4

R6

T5

T3

P4

R2

R3

8

C6

43

Not Bonded

(Preset to 0)

Not Bonded

(Preset to 0)

Not Bonded

(Preset to 0)

Not Bonded

(Preset to 0)

Not Bonded

(Preset to 0)

P2

9

A6

44

10

T6

45

11

Not Bonded

(Preset to 0)

Not Bonded

(Preset to 0)

Not Bonded

(Preset to 0)

D6

E7

F6

G7

46

12

47

13

48

N1

14

15

16

17

49

50

51

52

M2

L1

K2

Not Bonded

(Preset to 1)

H1

G2

E2

D1

Not Bonded

(Preset to 0)

Not Bonded

(Preset to 0)

Not Bonded

(Preset to 0)

Not Bonded

(Preset to 0)

Not Bonded

(Preset to 0)

Not Bonded

(Preset to 0)

18

19

20

21

22

H6

T7

K7

L6

N6

53

54

55

56

57

23

P7

58

24

Not Bonded

(Preset to 0)

Not Bonded

(Preset to 0)

Not Bonded

(Preset to 0)

Not Bonded

(Preset to 0)

Not Bonded

(Preset to 0)

Not Bonded

(Preset to 0)

Not Bonded

(Preset to 0)

B5

B3

C5

59

25

60

26

61

Not Bonded

(Preset to 0)

27

62

A5

28

63

A3

29

30

31

64

65

66

E4

B2

Not Bonded

(Preset to 0)

G3

Not Bonded

(Preset to 0)

L5

B6

32

33

C3

C2

67

68

34

35

A2

T2

69

70

相關PDF資料 |

PDF描述 |

|---|---|

| CY7C1372C-250BZI | 512K x 36/1M x 18 Pipelined SRAM with NoBL Architecture |

| CY7C1370D-225BGC | 18-Mbit (512K X 36/1M X 18) Pipelined SRAM with NoBL Architecture |

| CY7C1370D-250AXI | 18-Mbit (512K X 36/1M X 18) Pipelined SRAM with NoBL Architecture |

| CY7C1370D-250BGC | 18-Mbit (512K X 36/1M X 18) Pipelined SRAM with NoBL Architecture |

| CY7C1370D-250BGI | 18-Mbit (512K X 36/1M X 18) Pipelined SRAM with NoBL Architecture |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1372C-167AIT | 制造商:Cypress Semiconductor 功能描述:SRAM Chip Sync Dual 3.3V 18M-Bit 1M x 18 3.4ns 100-Pin TQFP T/R |

| CY7C1372C-167BGC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1372C167BZC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1372C-167BZC | 制造商:Cypress Semiconductor 功能描述:SRAM Chip Sync Single 3.3V 18M-Bit 1M x 18 3.4ns 165-Pin FBGA 制造商:Cypress Semiconductor 功能描述:SRAM Chip Sync Dual 3.3V 18M-Bit 1M x 18 3.4ns 165-Pin FBGA |

| CY7C1372CV25-167BZC | 制造商:Cypress Semiconductor 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。