- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359518 > CY7C1360B-166BGI (CYPRESS SEMICONDUCTOR CORP) CONNECTOR ACCESSORY PDF資料下載

參數(shù)資料

| 型號(hào): | CY7C1360B-166BGI |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | DRAM |

| 英文描述: | CONNECTOR ACCESSORY |

| 中文描述: | 256K X 36 CACHE SRAM, 3.5 ns, PBGA119 |

| 封裝: | 14 X 22 MM, 2.40 MM HEIGHT, PLASTIC, BGA-119 |

| 文件頁(yè)數(shù): | 11/34頁(yè) |

| 文件大小: | 895K |

| 代理商: | CY7C1360B-166BGI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)當(dāng)前第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)

CY7C1360B

CY7C1362B

Document #: 38-05291 Rev. *C

Page 11 of 34

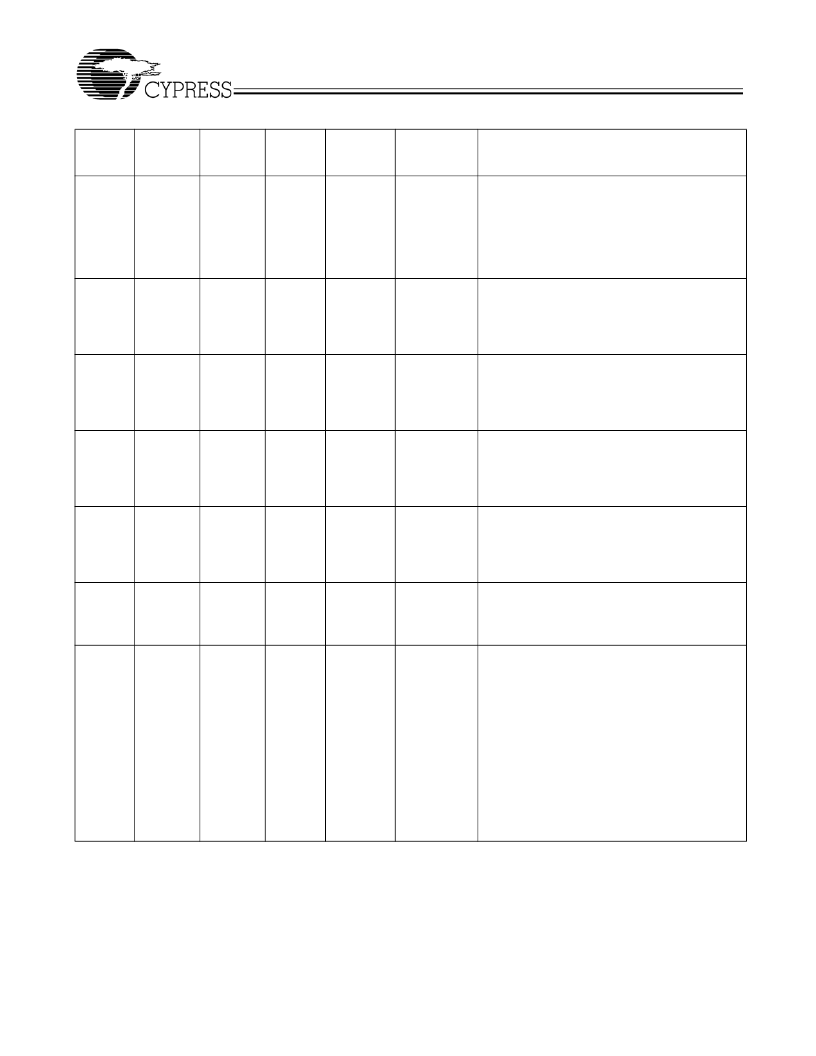

V

DDQ

4,11,20,27,

54,61,70,

77

4,11,20,27,

54,61,70,

77

A1,A7,F1,

F7,J1,J7,

M1,M7,

U1,U7

C3,C9,D3,

D9,E3,E9,

F3,F9,G3,

G9,J3,J9,

K3,K9,L3,

L9,M3,M9,

N3,N9

I/O Power

Supply

Power supply for the I/O circuitry

.

MODE

31

31

R3

R1

Input-

Static

Selects Burst Order

. When tied to GND selects

linear burst sequence. When tied to V

DD

or left

floating selects interleaved burst sequence. This is

a strap pin and should remain static during device

operation. Mode pin has an internal pull-up.

TDO

-

-

U5

P7

JTAG serial

output

Synchronous

Serial data-out to the JTAG circuit

. Delivers data

on the negative edge of TCK. If the JTAG feature

is not being utilized, this pin should be left uncon-

nected. This pin is not available on TQFP

packages.

TDI

-

-

U3

P5

JTAG serial

input

Synchronous

Serial data-In to the JTAG circuit

. Sampled on

the rising edge of TCK. If the JTAG feature is not

being utilized, this pin can be left floating or con-

nected to V

DD

through a pull-up resistor. This pin

is not available on TQFP packages.

TMS

-

-

U2

R5

JTAG serial

input

Synchronous

Serial data-In to the JTAG circuit

. Sampled on

the rising edge of TCK. If the JTAG feature is not

being utilized, this pin can be disconnected or con-

nected to V

DD

. This pin is not available on TQFP

packages.

TCK

-

-

U4

R7

JTAG-Clock

Clock input to the JTAG circuitry

. If the JTAG

feature is not being utilized, this pin must be

connected to V

SS

. This pin is not available on

TQFP packages.

NC

1,2,3,6,7,

14,16,25,

28,29,30,

38,39,42,

51,52,53,

56,57,66,

75,78,79,

95,96

1,2,3,6,7,

14,16,25,

28,29,30,

38,39,42,

43,51,52,

53,56,57,

66,75,78,

79,95,96

B1,B7,

C1,C7,

D2,D4,

D7,E1,

E6,H2,

F2,G1,

G6,H7,

J3,J5,K1,

K6,L4,L2,

L7,M6,

N2,L7,P1,

P6,R1,

R5,R7,

T1,T4,U6

A5,B1,B4,

C1,C2,C10,

D1,D10,

E1,E10,F1,

F10,G1,

G10,H1,H3,

H9,H10,J2,

J11,K2,

K11,L2,L1,

M2,M11,

N2,N7,N10,

N5,N11,P1,

A1,B11,P2,

R2,N6

-

No Connects

. Not internally connected to the die.

CY7C1362B–Pin Definitions

(continued)

Name

TQFP

3-Chip

Enable

TQFP

2-Chip

Enable

BGA

fBGA

I/O

Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C138AV-20JC | 3.3V 4K/8K/16K/32K x 8/9 Dual-Port Static RAM |

| CY7C138AV-25JC | 3.3V 4K/8K/16K/32K x 8/9 Dual-Port Static RAM |

| DR045 | DIGITAL FREQUENCY DISCRIMINATORS |

| DS12887A | Real Time Clock |

| DS1993L-F5 | 1kbit/4kbit Memory iButtonTM DS1994 4-kbit Plus Time Memory iButtonTM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1360B-200AC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1360B-200AJC | 制造商:Cypress Semiconductor 功能描述:SRAM SYNC SGL 3.3V 9MBIT 256KX36 3NS 100TQFP - Bulk |

| CY7C1360B-200BGC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1360B-200BGCT | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1360B-200BZC | 制造商:Rochester Electronics LLC 功能描述:8M- 256KX36 3.3V PIPELINE 1CD-SYNCHRONOUS SRAM - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。