- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379089 > CY7C1320BV18 (Cypress Semiconductor Corp.) 18-Mbit DDR-II SRAM 2-Word Burst Architecture(2字Burst結(jié)構(gòu),18-Mbit DDR-II SRAM) PDF資料下載

參數(shù)資料

| 型號(hào): | CY7C1320BV18 |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | 18-Mbit DDR-II SRAM 2-Word Burst Architecture(2字Burst結(jié)構(gòu),18-Mbit DDR-II SRAM) |

| 中文描述: | 18兆位的DDR - II SRAM的2字突發(fā)架構(gòu)(2字突發(fā)結(jié)構(gòu),18 -兆位的DDR - II SRAM的) |

| 文件頁數(shù): | 6/28頁 |

| 文件大小: | 469K |

| 代理商: | CY7C1320BV18 |

第1頁第2頁第3頁第4頁第5頁當(dāng)前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

CY7C1316BV18

CY7C1916BV18

CY7C1318BV18

CY7C1320BV18

Document Number: 38-05621 Rev. *C

Page 6 of 28

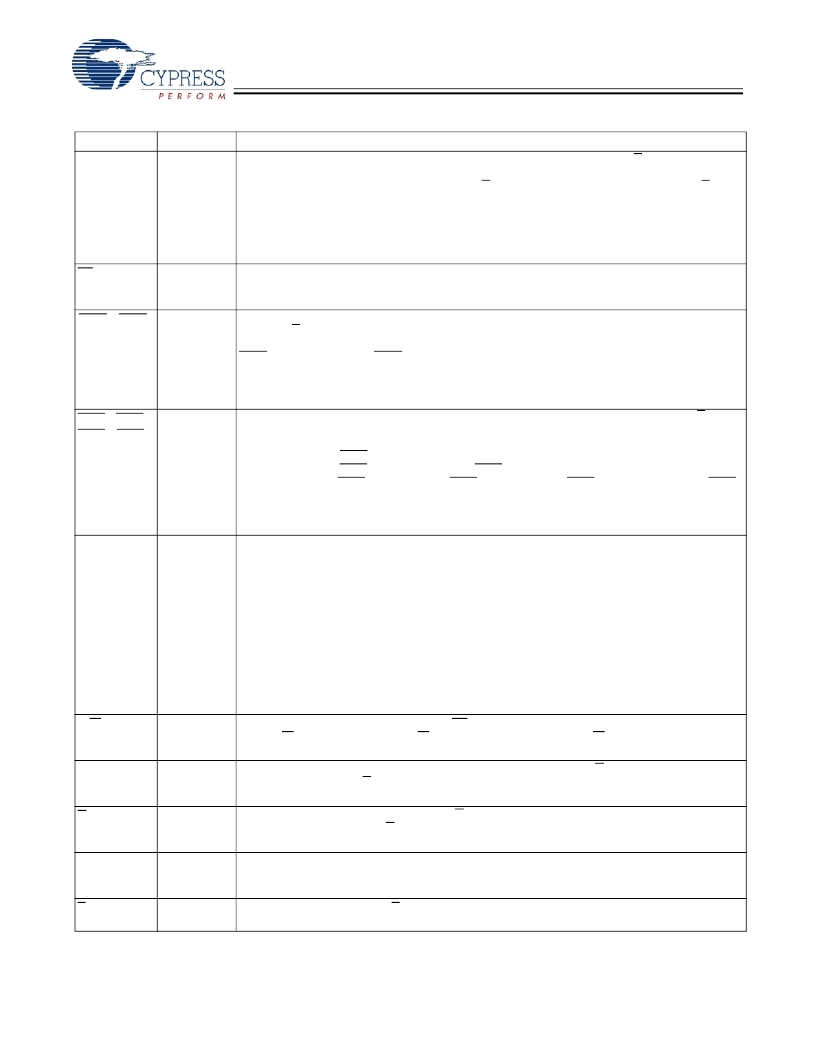

Pin Definitions

Pin Name

DQ

[x:0]

I/O

Pin Description

Input/Output-

Synchronous

Data Input/Output signals

. Inputs are sampled on the rising edge of K and K clocks during valid

Write operations. These pins drive out the requested data during a Read operation. Valid data is

driven out on the rising edge of both the C and C clocks during Read operations or K and K when

in single clock mode. When read access is deselected, Q

[x:0]

are automatically tri-stated.

CY7C1316BV18

DQ

[7:0]

CY7C1916BV18

DQ

[8:0]

CY7C1318BV18

DQ

[17:0]

CY7C1320BV18

DQ

[35:0]

Synchronous Load

. This input is brought LOW when a bus cycle sequence is to be defined.

This definition includes address and Read/Write direction. All transactions operate on a burst of

2 data.

Nibble Write Select 0, 1

active LOW

(CY7C1316BV18 only)

. Sampled on the rising edge of

the K and K clocks during Write operations. Used to select which nibble is written into the device

during the current portion of the Write operations. Nibbles not written remain unaltered.

NWS

0

controls D

[3:0]

and NWS

1

controls D

[7:4]

.

All the Nibble Write Selects are sampled on the same edge as the data. Deselecting a Nibble

Write Select will cause the corresponding nibble of data to be ignored and not written into the

device.

Byte Write Select 0, 1, 2, and 3

active LOW

. Sampled on the rising edge of the K and K clocks

during Write operations. Used to select which byte is written into the device during the current

portion of the Write operations. Bytes not written remain unaltered.

CY7C1916BV18

BWS

0

controls D

[8:0]

CY7C1318BV18

BWS

0

controls D

[8:0]

and BWS

1

controls D

[17:9].

CY7C1320BV18

BWS

0

controls D

[8:0]

, BWS

1

controls D

[17:9]

, BWS

2

controls D

[26:18]

and BWS

3

controls D

[35:27]

.

All the Byte Write Selects are sampled on the same edge as the data. Deselecting a Byte Write

Select will cause the corresponding byte of data to be ignored and not written into the device.

Address Inputs

. These address inputs are multiplexed for both Read and Write operations.

Internally, the device is organized as 2M x 8 (2 arrays each of 1M x 8) for CY7C1316BV18 and

2M x 9 (2 arrays each of 1M x 9) for CY7C1916BV18, a single 1M x 18 array for CY7C1318BV18,

and a single array of 512K x 36 for CY7C1320BV18.

CY7C1316BV18 – Since the least significant bit of the address internally is a “0,” only 20 external

address inputs are needed to access the entire memory array.

CY7C1916BV18 – Since the least significant bit of the address internally is a “0,” only 20 external

address inputs are needed to access the entire memory array.

CY7C1318BV18 – A0 is the input to the burst counter. These are incremented in a linear fashion

internally. 20 address inputs are needed to access the entire memory array.

CY7C1320BV18 – A0 is the input to the burst counter. These are incremented in a linear fashion

internally. 19 address inputs are needed to access the entire memory array. All the address inputs

are ignored when the appropriate port is deselected.

LD

Input-

Synchronous

NWS

0

, NWS

1

Input-

Synchronous

BWS

0

, BWS

1

,

BWS

2

, BWS

3

Input-

Synchronous

A, A0

Input-

Synchronous

R/W

Input-

Synchronous

Synchronous Read/Write Input

. When LD is LOW, this input designates the access type (Read

when R/W is HIGH, Write when R/W is LOW) for loaded address. R/W must meet the set-up and

hold times around edge of K.

Positive Input Clock for Output Data.

C is used in conjunction with C to clock out the Read data

from the device. C and C can be used together to deskew the flight times of various devices on

the board back to the controller. See application example for further details.

Negative Input Clock for Output Data

. C is used in conjunction with C to clock out the Read

data from the device. C and C can be used together to deskew the flight times of various devices

on the board back to the controller. See application example for further details.

Positive Input Clock Input

. The rising edge of K is used to capture synchronous inputs to the

device and to drive out data through Q

[x:0]

when in single clock mode. All accesses are initiated

on the rising edge of K.

C

Input-

Clock

C

Input-

Clock

K

Input-

Clock

K

Input-

Clock

Negative Input Clock Input

. K is used to capture synchronous data being presented to the device

and to drive out data through Q

[x:0]

when in single clock mode.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C1316BV18 | 18-Mbit DDR-II SRAM 2-Word Burst Architecture(2字Burst結(jié)構(gòu),18-Mbit DDR-II SRAM) |

| CY7C1318BV18 | 18-Mbit DDR-II SRAM 2-Word Burst Architecture(2字Burst結(jié)構(gòu),18-Mbit DDR-II SRAM) |

| CY7C192 | 64K x 4 Static RAM with Separate I/O(帶獨(dú)立的輸入/輸出口的64K x 4靜態(tài) RAM) |

| CY7C194B | 256 Kb (64K x 4) Static RAM |

| CY7C194B-15PC | 256 Kb (64K x 4) Static RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1320BV18-167BZC | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 512Kx36 1.8V COM DDR II 靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1320BV18-167BZCT | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 512Kx36 1.8V COM DDR II 靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1320BV18-167BZI | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1320BV18200BZC | 制造商:Cypress Semiconductor 功能描述:SRAM Chip Sync Single 1.8V 18M-Bit 512K x 36 0.45ns 165-Pin FBGA |

| CY7C1320BV18-200BZC | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 512Kx36 1.8V COM DDR II 靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。