- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379058 > CY7C1245V18 (Cypress Semiconductor Corp.) 36-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.0 Cycle Read Latency) PDF資料下載

參數(shù)資料

| 型號: | CY7C1245V18 |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | 36-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.0 Cycle Read Latency) |

| 中文描述: | 36兆位的國防評估報告⑩- II SRAM的4字突發(fā)架構(gòu)(2.0周期讀寫延遲) |

| 文件頁數(shù): | 27/28頁 |

| 文件大?。?/td> | 1042K |

| 代理商: | CY7C1245V18 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當前第27頁第28頁

CY7C1241V18

CY7C1256V18

CY7C1243V18

CY7C1245V18

Document Number: 001-06365 Rev. *C

Page 27 of 28

Cypress Semiconductor Corporation, 2006-2007. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the

use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to

be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its

products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress

products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

QDR RAMs and Quad Data Rate RAMs comprise a new family of products developed by Cypress, IDT, NEC, Renesas, andSamsung. All other trademarks or registered trademarks referenced

herein are property of the respective corporations.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and

foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create

derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only

in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except

as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WAR-

RANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein.

Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in

life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application

implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

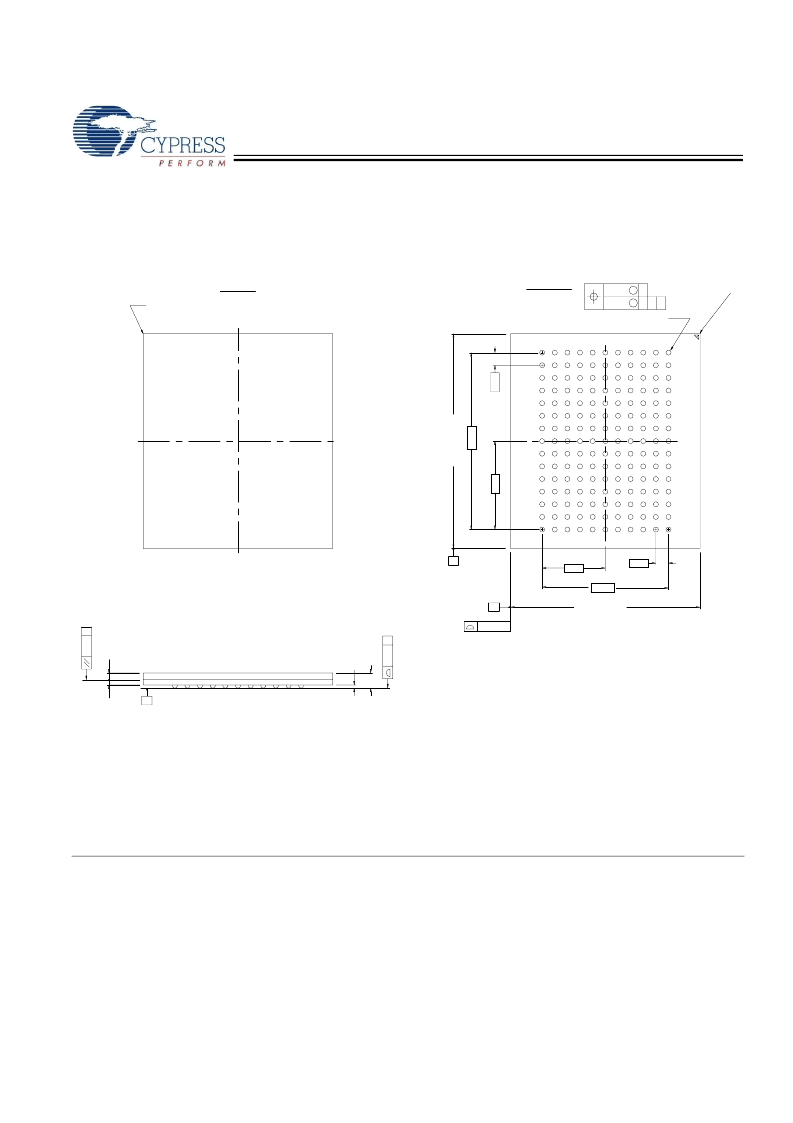

Package Diagram

Figure 5. 165-ball FBGA (15 x 17 x 1.40 mm), 51-85195

!

0).#/2.%2

8

-#!"

-#

"

!

8

-

3%!4).'0,!.%

#

#

0).#/2.%2

4/06)%7

"/44/-6)%7

"

#

$

%

&

'

(

*

+

,

-

.

0

2

0

2

+

-

.

,

*

(

'

&

%

$

#

"

!

#

3/,$%20!$490%./.3/,$%2-!3+$%&).%$.3-$

./4%3

0!#+!'%7%)'(4G

*%$%#2%&%2%.#%-/$%3)'.#

0!#+!'%#/$%""!$

51-85195-*A

[+] Feedback

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C1245V18-300BZC | 36-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.0 Cycle Read Latency) |

| CY7C1245V18-300BZI | 36-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.0 Cycle Read Latency) |

| CY7C1245V18-300BZXC | 36-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.0 Cycle Read Latency) |

| CY7C1245V18-300BZXI | 36-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.0 Cycle Read Latency) |

| CY7C1256V18 | 36-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.0 Cycle Read Latency) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1245V18-375BZC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1245XC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C12481KV18-400BZC | 功能描述:靜態(tài)隨機存取存儲器 2M X 18 400MHz DDR II+ 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C12481KV18-400BZXC | 功能描述:IC SRAM 36MBIT 400MHZ 165-FPBGA RoHS:是 類別:集成電路 (IC) >> 存儲器 系列:- 標準包裝:150 系列:- 格式 - 存儲器:EEPROMs - 串行 存儲器類型:EEPROM 存儲容量:4K (2 x 256 x 8) 速度:400kHz 接口:I²C,2 線串口 電源電壓:2.5 V ~ 5.5 V 工作溫度:-40°C ~ 85°C 封裝/外殼:8-VFDFN 裸露焊盤 供應商設(shè)備封裝:8-DFN(2x3) 包裝:管件 產(chǎn)品目錄頁面:1445 (CN2011-ZH PDF) |

| CY7C1248KV18-400BZC | 功能描述:靜態(tài)隨機存取存儲器 36MB (2Mx18) 1.8v 400MHz DDR II 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復。