- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378497 > CY7C1176V18-300BZXC (CYPRESS SEMICONDUCTOR CORP) 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.5 Cycle Read Latency) PDF資料下載

參數(shù)資料

| 型號(hào): | CY7C1176V18-300BZXC |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | DRAM |

| 英文描述: | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.5 Cycle Read Latency) |

| 中文描述: | 2M X 9 QDR SRAM, 0.45 ns, PBGA165 |

| 封裝: | 13 X 15 MM, 1.40 MM HEIGHT, LEAD FREE, MO-216, FPBGA-165 |

| 文件頁(yè)數(shù): | 2/29頁(yè) |

| 文件大小: | 956K |

| 代理商: | CY7C1176V18-300BZXC |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)

CY7C1161V18

CY7C1176V18

CY7C1163V18

CY7C1165V18

Document Number: 001-06582 Rev. *C

Page 2 of 29

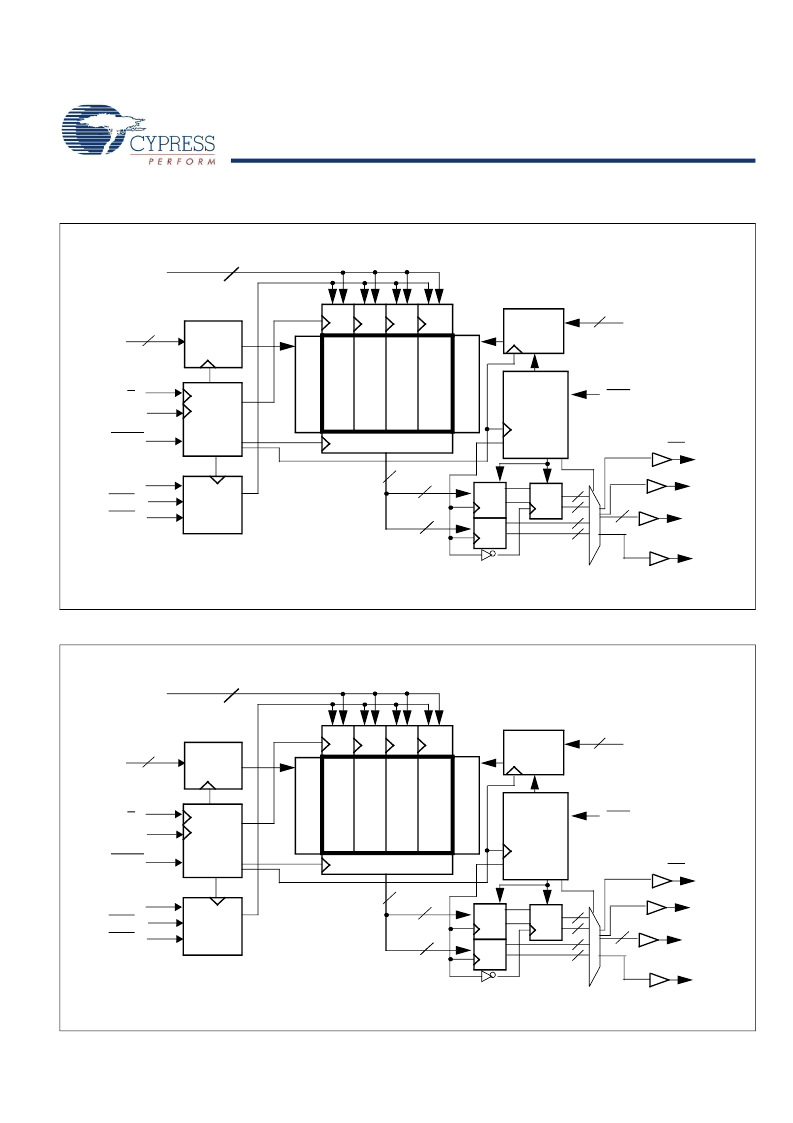

Logic Block Diagram (CY7C1161V18)

Logic Block Diagram (CY7C1176V18)

5

CLK

Gen.

A

(18:0)

K

K

Control

Logic

Address

Register

D

[7:0]

R

Read Data Reg.

RPS

WPS

NWS

[1:0]

Q

[7:0]

Control

Logic

Address

Register

Reg.

Reg.

Reg.

16

19

8

32

8

V

REF

W

Write

Reg

16

A

(18:0)

19

5

5

5

Write

Reg

Write

Reg

Write

Reg

8

CQ

CQ

DOFF

QVLD

5

CLK

Gen.

A

(18:0)

K

K

Control

Logic

Address

Register

D

[8:0]

R

Read Data Reg.

RPS

WPS

BWS

[0]

Q

[8:0]

Control

Logic

Address

Register

Reg.

Reg.

Reg.

18

19

9

36

9

V

REF

W

Write

Reg

18

A

(18:0)

19

5

5

5

Write

Reg

Write

Reg

Write

Reg

9

CQ

CQ

DOFF

QVLD

[+] Feedback

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C1176V18-300BZXI | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.5 Cycle Read Latency) |

| CY7C1176V18-333BZC | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.5 Cycle Read Latency) |

| CY7C1176V18-333BZI | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.5 Cycle Read Latency) |

| CY7C1176V18-333BZXC | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.5 Cycle Read Latency) |

| CY7C1176V18-333BZXI | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.5 Cycle Read Latency) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1214F-100AC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1214F-100ACT | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1215F-166AC | 制造商:Rochester Electronics LLC 功能描述:1MB (32K X 32) 3.3V PIPELINE SCD - Bulk 制造商:Cypress Semiconductor 功能描述: |

| CY7C1215H-166AXC | 制造商:Cypress Semiconductor 功能描述:SRAM SYNC SGL 3.3V 1MBIT 32KX32 3.5NS 100TQFP - Bulk |

| CY7C1217H-133AXC | 制造商:Cypress Semiconductor 功能描述:SRAM SYNC QUAD 3.3V 1.125MBIT 32KX36 7.5NS 100TQFP - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。