- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379057 > CY7C1141V18-300BZXI (CYPRESS SEMICONDUCTOR CORP) 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.0 Cycle Read Latency) PDF資料下載

參數(shù)資料

| 型號: | CY7C1141V18-300BZXI |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | DRAM |

| 英文描述: | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.0 Cycle Read Latency) |

| 中文描述: | 2M X 8 QDR SRAM, 0.45 ns, PBGA165 |

| 封裝: | 13 X 15 MM, 1.40 MM HEIGHT, LEAD FREE, MO-216, FPBGA-165 |

| 文件頁數(shù): | 7/28頁 |

| 文件大小: | 954K |

| 代理商: | CY7C1141V18-300BZXI |

第1頁第2頁第3頁第4頁第5頁第6頁當前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

CY7C1141V18

CY7C1156V18

CY7C1143V18

CY7C1145V18

Document Number: 001-06583 Rev. *C

Page 7 of 28

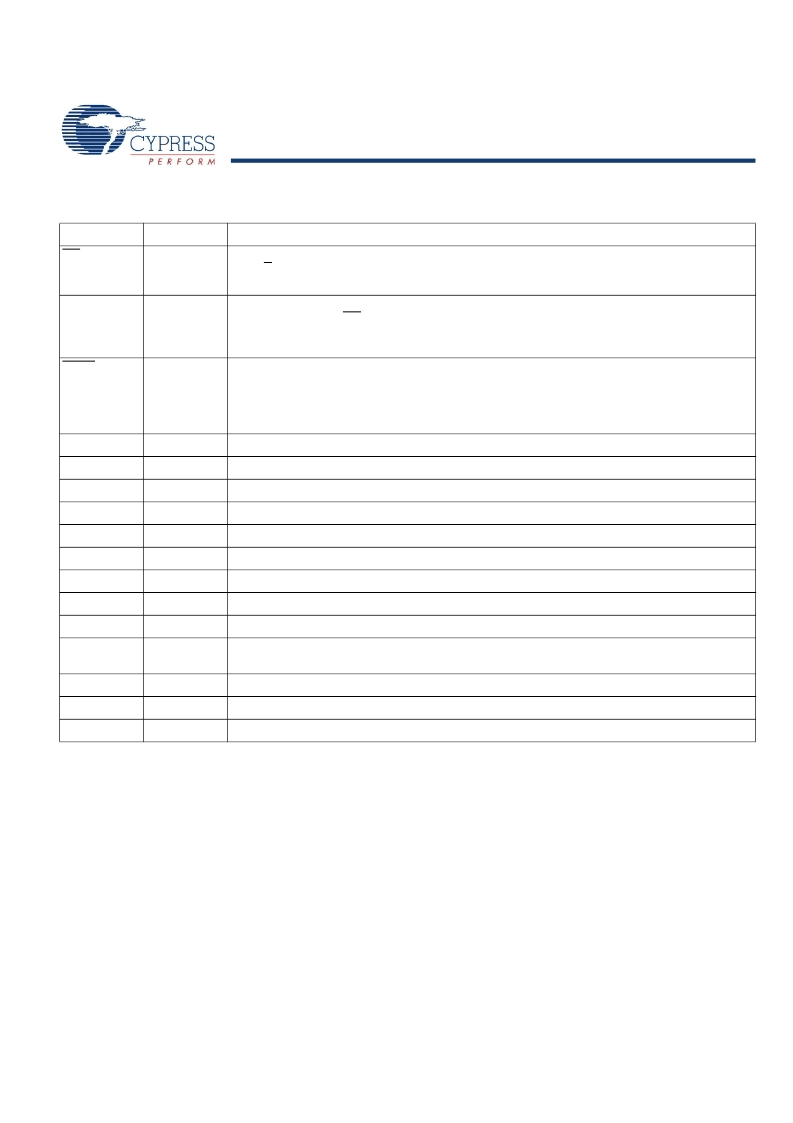

CQ

Echo Clock

Synchronous Echo Clock Outputs

. This is a free running clock and is synchronized to the input

clock (K) of the QDR-II+. The timings for the echo clocks are shown in the

“Switching Characteristics”

on page 23.

ZQ

Input

Output Impedance Matching Input

. This input is used to tune the device outputs to the system data

bus impedance. CQ, CQ and Q

[x:0]

output impedance are set to 0.2 x RQ, where RQ is a resistor

connected between ZQ and ground. Alternatively, connect this pin directly to V

DDQ

, which enables

the minimum impedance mode. This pin cannot be connected directly to GND or left unconnected.

DOFF

Input

DLL Turn Off

Active LOW

. Connecting this pin to ground turns off the DLL inside the device. The

timings in the DLL turned off operationis different from those listed in this data sheet. For normal

operation, connect this pin to a pull up through a 10 K

or less pull up resistor. The device behaves

in QDR-I mode when the DLL is turned off. In this mode, operate the device at a frequency of up to

167 MHz with QDR-I timing.

TDO

Output

TDO for JTAG

.

TCK

Input

TCK pin for JTAG

.

TDI

Input

TDI pin for JTAG

.

TMS

Input

TMS pin for JTAG

.

NC

N/A

Not connected to the die

. Tie to any voltage level.

NC/36M

N/A

Not connected to the die

. Tie to any voltage level.

NC/72M

N/A

Not connected to the die

. Tie to any voltage level.

NC

/144M

N/A

Not connected to the die

. Tie to any voltage level.

NC

/288M

N/A

Not connected to the die

. Tie to any voltage level.

V

REF

Input-

Reference

Reference Voltage Input

. Static input used to set the reference level for HSTL inputs, outputs, and

AC measurement points.

V

DD

Power Supply

Power supply inputs to the core of the device

.

V

SS

Ground

Ground for the device

.

V

DDQ

Power Supply

Power supply inputs for the outputs of the device

.

Pin Definitions

(continued)

Pin Name

IO

Pin Description

[+] Feedback

相關PDF資料 |

PDF描述 |

|---|---|

| CY7C1143V18 | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.0 Cycle Read Latency) |

| CY7C1143V18-300BZC | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.0 Cycle Read Latency) |

| CY7C1143V18-300BZI | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.0 Cycle Read Latency) |

| CY7C1143V18-300BZXC | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.0 Cycle Read Latency) |

| CY7C1143V18-300BZXI | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.0 Cycle Read Latency) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1143KV18-400BZC | 功能描述:靜態(tài)隨機存取存儲器 18MB (1Mx18) 1.8v 400MHz DDR II 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1143KV18-400BZI | 功能描述:靜態(tài)隨機存取存儲器 18MB (1Mx18) 1.8v 400MHz DDR II 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1143KV18-450BZC | 功能描述:靜態(tài)隨機存取存儲器 18MB (1Mx18) 1.8v 450MHz DDR II 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1145KV18-400BZXC | 功能描述:靜態(tài)隨機存取存儲器 18MB (512Kx36) 1.8v 400MHz QDR II 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1145KV18-400BZXCT | 功能描述:靜態(tài)隨機存取存儲器 18Mb 1.8V 512Kb x 36 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復。