- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379057 > CY7C1006 (Cypress Semiconductor Corp.) 256K x 4 Static RAM(256K x4 靜態(tài) RAM) PDF資料下載

參數(shù)資料

| 型號: | CY7C1006 |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | 256K x 4 Static RAM(256K x4 靜態(tài) RAM) |

| 中文描述: | 256K × 4靜態(tài)存儲器(256K x4靜態(tài)內(nèi)存) |

| 文件頁數(shù): | 1/8頁 |

| 文件大?。?/td> | 203K |

| 代理商: | CY7C1006 |

256K x 4 Static RAM

CY7C106

CY7C1006

Cypress Semiconductor Corporation

3901 North First Street

San Jose

CA 95134

408-943-2600

July 9, 1998

Features

High speed

—t

AA

=

12 ns

CMOS for optimum speed/power

Low active power

—910 mW

Low standby power

—275 mW

2.0V data retention (optional)

—

100

μ

W

Automatic power-down when deselected

TTL-compatible inputs and outputs

Functional Description

The CY7C106 and CY7C1006 are high-performance CMOS

static RAMs organized as 262,144 words by 4 bits. Easy mem-

ory expansion is provided by an active LOW chip enable (CE),

an active LOW output enable (OE), and three-state drivers.

These devices have an automatic power-down feature that re-

duces power consumption by more than 65% when the devic-

es are deselected.

Writing to the devices is accomplished by taking chip enable

(CE) and write enable (WE) inputs LOW. Data on the four I/O

pins (I/O

0

through I/O

3

) is then written into the location speci-

fied on the address pins (A

0

through A

17

).

Reading from the devices is accomplished by taking chip en-

able (CE) and output enable (OE) LOW while forcing write en-

able (WE) HIGH. Under these conditions, the contents of the

memory location specified by the address pins will appear on

the four I/O pins.

The four input/output pins (I/O

0

through I/O

3

) are placed in a

high-impedance state when the devices are deselected (CE

HIGH), the outputs are disabled (OE HIGH), or during a write

operation (CE and WE LOW).

The CY7C106 is available in a standard 400-mil-wide SOJ; the

CY7C1006 is available in a standard 300-mil-wide SOJ.

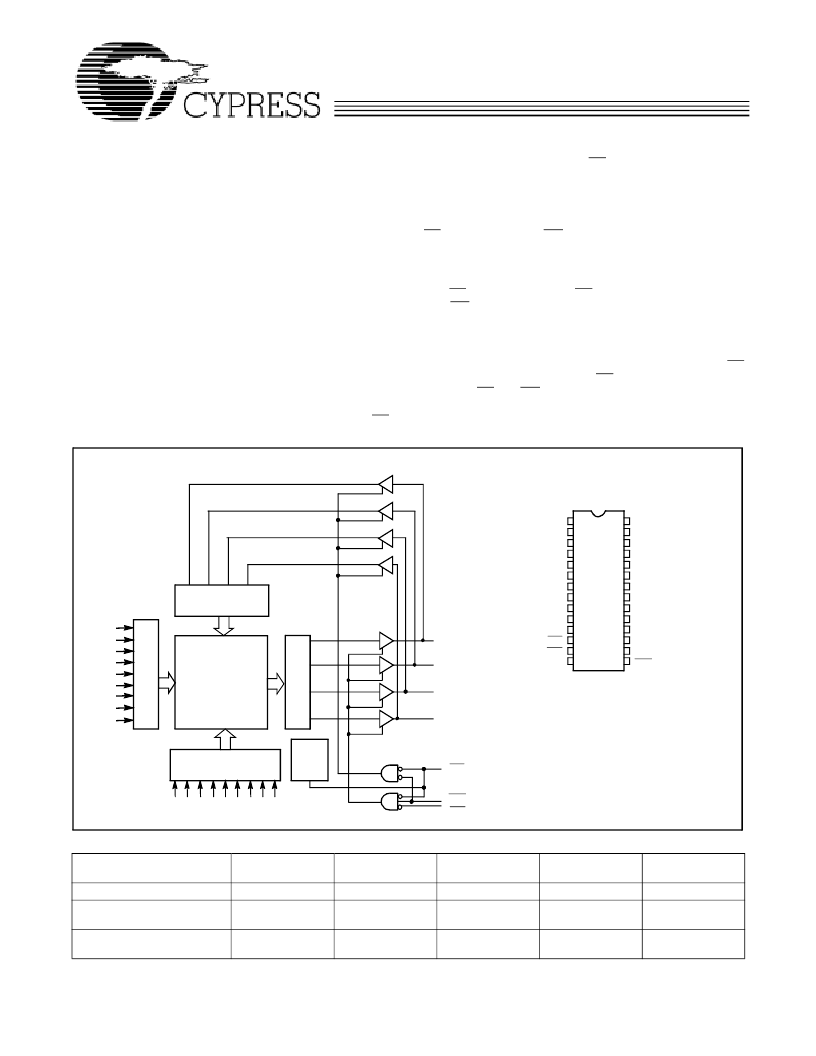

Logic Block Diagram

Pin Configuration

C106–1

C106–2

512 x 512 x 4

ARRAY

A

1

A

2

A

3

A

4

A

5

A

0

A

1

A

1

A

1

A

1

A

1

COLUMN

DECODER

R

S

POWER

DOWN

OE

INPUTBUFFER

A

1

A

1

A

1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

20

19

18

17

21

24

23

22

Top View

SOJ

25

28

27

26

GND

A

1

A

2

A

3

A

4

A

5

A

6

A

7

A

8

A

9

A

CE

OE

A

17

A

16

A

15

A

14

A

13

A

12

A

11

V

CC

I/O

3

I/O

2

I/O

1

I/O

0

WE

A

0

NC

WE

CE

I/O

0

I/O

1

I/O

2

I/O

3

A

6

A

7

A

8

A

9

Selection Guide

7C106-12

7C1006-12

12

165

7C106-15

7C1006-15

15

155

7C106-20

7C1006-20

20

145

7C106-25

7C1006-25

25

130

7C106-35

35

125

Maximum Access Time (ns)

Maximum Operating

Current (mA)

Maximum Standby

Current (mA)

50

30

30

30

25

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C1146V18 | 18-Mbit DDR-II+ SRAM 2-Word Burst Architecture (2.0 Cycle Read Latency) |

| CY7C1150V18-333BZXC | 18-Mbit DDR-II+ SRAM 2-Word Burst Architecture (2.0 Cycle Read Latency) |

| CY7C1150V18-333BZXI | 18-Mbit DDR-II+ SRAM 2-Word Burst Architecture (2.0 Cycle Read Latency) |

| CY7C1150V18-375BZC | 18-Mbit DDR-II+ SRAM 2-Word Burst Architecture (2.0 Cycle Read Latency) |

| CY7C1150V18-375BZI | 18-Mbit DDR-II+ SRAM 2-Word Burst Architecture (2.0 Cycle Read Latency) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1006B-15VC | 制造商:Cypress Semiconductor 功能描述:SRAM Chip Async Single 5V 1M-Bit 256K x 4-Bit 15ns 28-Pin SOJ 制造商:Rochester Electronics LLC 功能描述:1MB (256K X 4)- FAST ASYNCH SRAM - Bulk |

| CY7C1006B-15VCT | 制造商:Cypress Semiconductor 功能描述:SRAM Chip Async Single 5V 1M-Bit 256K x 4-Bit 15ns 28-Pin SOJ T/R 制造商:Cypress Semiconductor 功能描述:SRAM ASYNC SGL 5V 1MBIT 256K X 4 15NS 28PIN MLD SOJ - Tape and Reel 制造商:Rochester Electronics LLC 功能描述:1MB (256K X 4)- FAST ASYNCH SRAM - Bulk |

| CY7C1006B-15VXC | 功能描述:IC SRAM 1MBIT 15NS 28SOJ RoHS:是 類別:集成電路 (IC) >> 存儲器 系列:- 標(biāo)準(zhǔn)包裝:1,000 系列:- 格式 - 存儲器:RAM 存儲器類型:移動 SDRAM 存儲容量:256M(8Mx32) 速度:133MHz 接口:并聯(lián) 電源電壓:1.7 V ~ 1.95 V 工作溫度:-40°C ~ 85°C 封裝/外殼:90-VFBGA 供應(yīng)商設(shè)備封裝:90-VFBGA(8x13) 包裝:帶卷 (TR) 其它名稱:557-1327-2 |

| CY7C1006B-15VXCT | 制造商:Cypress Semiconductor 功能描述:SRAM ASYNC SGL 5V 1MBIT 256K X 4 15NS 28PIN MLD SOJ - Tape and Reel |

| CY7C1006B-20VC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。