- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379006 > CY28347ZCT (CYPRESS SEMICONDUCTOR CORP) Universal Single-chip Clock Solution for VIA P4M266/KM266 DDR Systems PDF資料下載

參數(shù)資料

| 型號: | CY28347ZCT |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | XO, clock |

| 英文描述: | Universal Single-chip Clock Solution for VIA P4M266/KM266 DDR Systems |

| 中文描述: | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封裝: | 6 X 14 MM, TSSOP-56 |

| 文件頁數(shù): | 5/22頁 |

| 文件大小: | 188K |

| 代理商: | CY28347ZCT |

CY28347

Document #: 38-07352 Rev. *C

Page 5 of 22

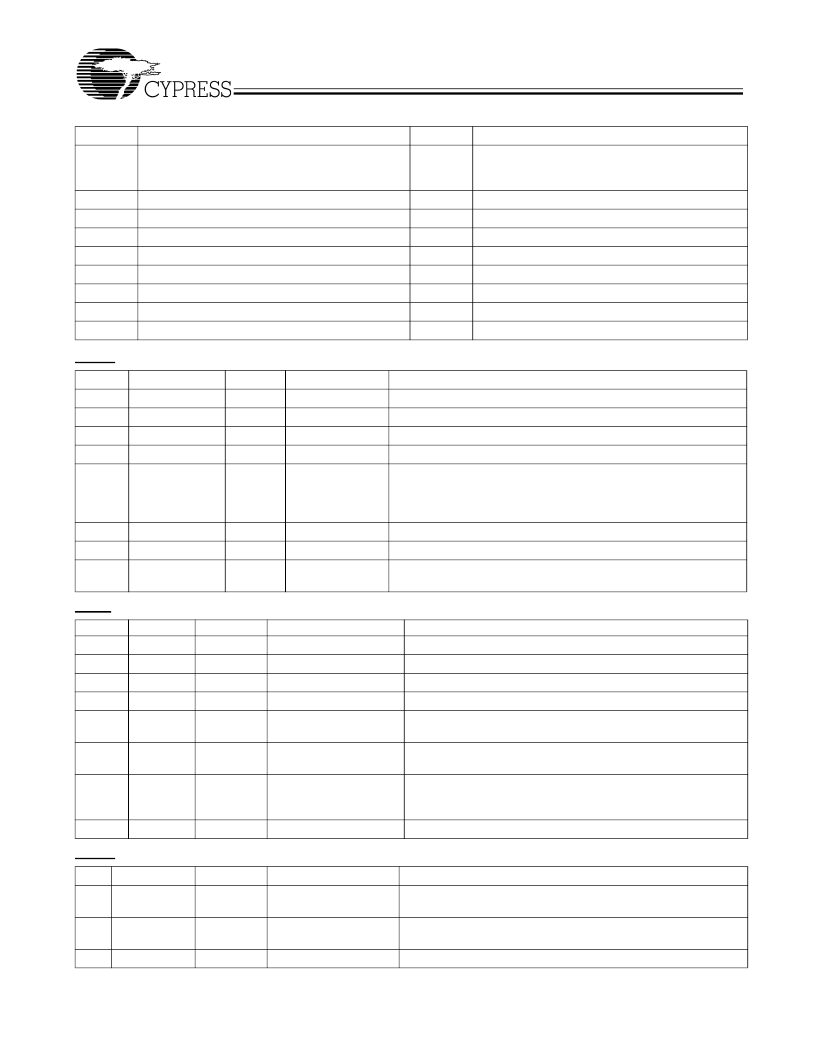

Byte 0: Frequency Select Register

10

Acknowledge from slave

10

Acknowledge from slave

11:18

Command Code - 8 bits

“

1xxxxxxx

”

stands for byte

operation bit[6:0] of the command code represents

the offset of the byte to be accessed

Acknowledge from slave

Data Byte from Master

–

8 Bits

Acknowledge from slave

Stop

11:18

Command Code - 8 bits

“

1xxxxxxx

”

stands for byte

operation bit[6:0] of the command code represents

the offset of the byte to be accessed

Acknowledge from slave

Repeat start

Slave address - 7 bits

Read

Acknowledge from slave

Data byte from slave - 8 bits

Not Acknowledge

Stop

19

19

20

20:27

28

29

21:27

28

29

30:37

38

39

Table 6. Byte Read and Byte Write Protocol

(continued)

Bit

7

6

5

4

3

@Pup

0

H/W Setting

H/W Setting

H/W Setting

0

Pin#

Name

Description

Reserved.

For Selecting Frequencies see

Table 1.

For Selecting Frequencies see

Table 1.

For Selecting Frequencies see

Table 1.

If this bit is programmed to

“

1,

”

it enables WRITES to bits (6:4,1) for

selecting the frequency via software (SMBus)

If this bit is programmed to a

“

0

”

it enables only READS of bits

(6:4,1), which reflect the hardware setting of FS(0:3).

Reserved

For Selecting frequencies in

Table 1

.

Only for reading the hardware setting of the CPU interface mode,

status of SELP4_K7# strapping.

21

10

1

FS2

FS1

FS0

2

1

0

H/W Setting

H/W Setting

H/W Setting

11

20

7

Reserved

FS3

SELP4_K7#

Byte 1: CPU Clocks Register

Bit

7

6

5

4

3

@Pup

0

1

1

1

1

Pin#

Name

Description

SSMODE

SSCG

SST1

SST0

CPUCS_T/C_ EN#

0 = Down Spread. 1 = Center Spread. See

Table 9

.

1 = Enable (default). 0 = Disable

Select spread bandwidth. See

Table 9

.

Select spread bandwidth. See

Table 9

.

1 = output enabled (running). 0 = output disabled asynchronously

in a LOW state.

1 = output enabled (running). 0 = output disable asynchronously

in a LOW state.

In K7 mode, this bit is ignored. In P4 mode, when PD# asserted

LOW, 0 = drive CPUT to 2xIref and CPUC LOW and

1 = three-state CPUT and CPUC.

Only For reading the hardware setting of the Pin11 MULT0 value.

48,49

2

1

53,52

CPUOD_T/C_EN#

1

0

53,52

CPUT/C_PD_CNTRL

0

1

11

MULT0

Byte 2: PCI Clock Register

Bit

7

@Pup

0

Pin#

Name

PCI_DRV

Description

PCI clock output drive strength 0 = Normal, 1 = increase the drive

strength 20%.

1 = output enabled (running). 0 = output disabled asynchronously

in a LOW state.

Reserved, set = 1.

6

1

10

PCI_F

5

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY28347OC | Universal Single-chip Clock Solution for VIA P4M266/KM266 DDR Systems |

| CY28347OCT | Universal Single-chip Clock Solution for VIA P4M266/KM266 DDR Systems |

| CY28349B | FTG for Intel Pentium 4 CPU and Chipsets |

| CY28349BOC | FTG for Intel Pentium 4 CPU and Chipsets |

| CY28349BOCT | FTG for Intel Pentium 4 CPU and Chipsets |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY28349 | 制造商:SPECTRALINEAR 制造商全稱:SPECTRALINEAR 功能描述:FTG for Intel㈢ Pentium㈢ 4 CPU and Chipsets |

| CY28349B | 制造商:SPECTRALINEAR 制造商全稱:SPECTRALINEAR 功能描述:FTG for Intel㈢ Pentium㈢ 4 CPU and Chipsets |

| CY28349B_05 | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:FTG for Intel㈢ Pentium㈢ 4 CPU and Chipsets |

| CY28349BOC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY28349BOCT | 制造商:Rochester Electronics LLC 功能描述:FTG FOR INTEL 830M AND 845 CHIPSETS (CK-408) - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。