- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379006 > CY28347ZCT (CYPRESS SEMICONDUCTOR CORP) Universal Single-chip Clock Solution for VIA P4M266/KM266 DDR Systems PDF資料下載

參數(shù)資料

| 型號: | CY28347ZCT |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | XO, clock |

| 英文描述: | Universal Single-chip Clock Solution for VIA P4M266/KM266 DDR Systems |

| 中文描述: | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封裝: | 6 X 14 MM, TSSOP-56 |

| 文件頁數(shù): | 3/22頁 |

| 文件大小: | 188K |

| 代理商: | CY28347ZCT |

CY28347

Document #: 38-07352 Rev. *C

Page 3 of 22

6

MODE/AGP0

VDDAGP

I/O

PU

Power-on Bidirectional Input/Output

. At power-up, MODE is an input and

becomes AGP0 output after the power supply voltage crosses the input threshold

voltage. Must have 10K

resistor to V

SS

. See

Table 2

.

If pin 6 is pulled down at power on reset, then this pin becomes PCI_STP#

.

When PCI_STP# is asserted LOW, then all of the PCI signals, except the PCI_F,

stops at the next HIGH to LOW transition or stays LOW if it already is LOW.

Current reference programming input for CPU buffers

. A precise resistor is

attached to this pin, which is connected to the internal current reference.

I/O

Serial Data Input

. Conforms to the SMBus specification of a Slave

Receive/Transmit device. It is an input when receiving data. It is an open drain output

when acknowledging or transmitting data.

I

Serial Clock Input

. Conforms to the SMBus specification.

I

PU

management function.

I

2.5V CMOS type input to the DDR differential buffers

.

O

This is the single-ended, SDRAM buffered output of the signal applied at

BUF_IN

. It is in phase with the DDRT(0:5) signals.

3.3V power supply for AGP clocks

.

3.3V power supply for CPU (T: C) clocks

.

3.3V power supply for PCI clocks

.

3.3V power supply for REF clock

.

2.5V power supply for CPUCS_T/C clocks

.

3.3V power supply for 48M

.

3.3V Common power supply

.

2.5V power supply for DDR clocks

.

Ground for AGP clocks

.

Ground for PCI clocks

.

Ground for CPU (T:C) clocks

.

Ground for DDR clocks

.

Ground for 48M clock

.

Ground for CPUCS_T/C clocks

.

Common ground

.

8

PCI_STP#

VDDAGP

I

PU

25

IREF

I

28

SDATA

27

26

SCLK

PD#

When PD# is asserted LOW

, the device enters power down mode. See power

45

46

BUF_IN

FBOUT

5

51

16

55

50

22

23

34,40

9

13

54

33,39

19

47

24

VDDAGP

VDDC

VDDPCI

VDDR

VDDI

VDD48M

VDD

VDDD

VSSAGP

VSSPCI

VSSC

VSSD

VSS48M

VSSI

VSS

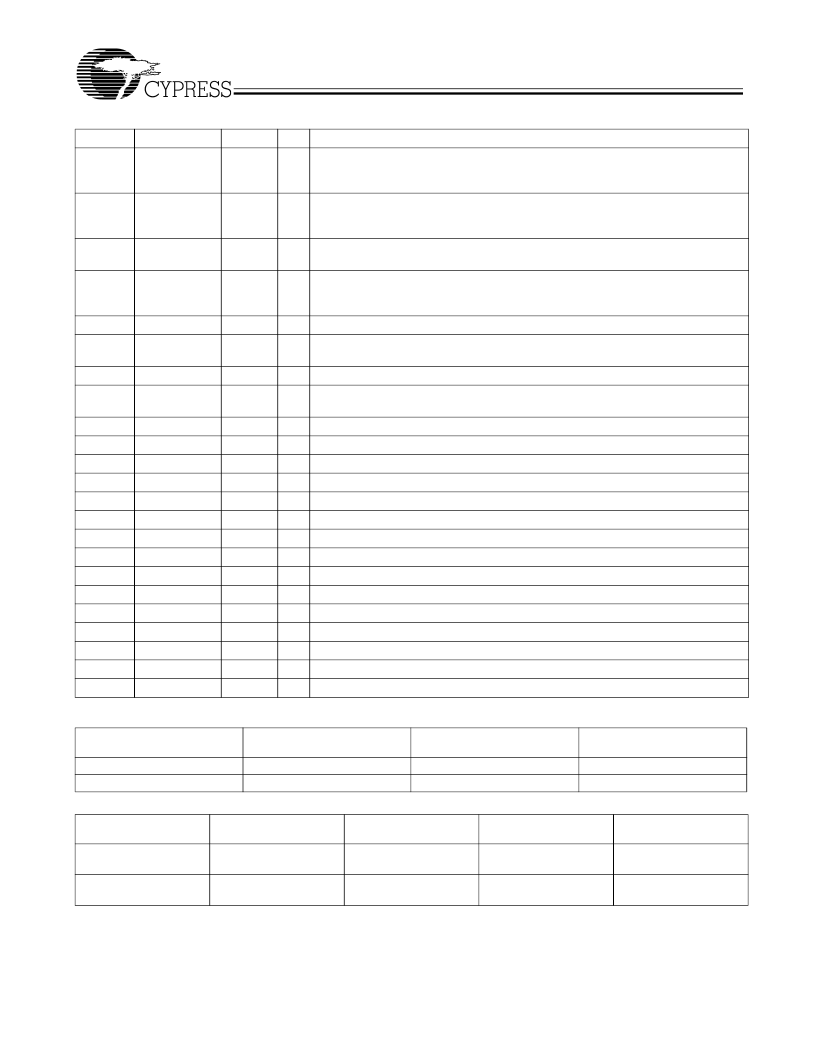

Pin Description

(continued)

[2]

Pin

Name

PWR

I/O

Description

Table 2. MODE Pin-Power Management Input Control

MODE, Pin 6

(Latched Input)

0

Invalid

Table 3. Swing Select Functions Through Hardware

Pin 26

Pin 18

Pin 8

PD#

Reserved

CPU_STP#

Reserved

PCI_STP#

Reserved

MULTSEL

0

Board Target

Trace/Term Z

50 Ohm

Reference R,

IREF = VDD/(3*Rr)

Rr = 221 1%,

IREF = 5.00 mA

Rr = 475 1%,

IREF = 2.32 mA

Output Current

IOH = 4* Iref

VOH@Z

1.0V@50

1

50 Ohm

IOH = 6* Iref

0.7V@50

相關PDF資料 |

PDF描述 |

|---|---|

| CY28347OC | Universal Single-chip Clock Solution for VIA P4M266/KM266 DDR Systems |

| CY28347OCT | Universal Single-chip Clock Solution for VIA P4M266/KM266 DDR Systems |

| CY28349B | FTG for Intel Pentium 4 CPU and Chipsets |

| CY28349BOC | FTG for Intel Pentium 4 CPU and Chipsets |

| CY28349BOCT | FTG for Intel Pentium 4 CPU and Chipsets |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| CY28349 | 制造商:SPECTRALINEAR 制造商全稱:SPECTRALINEAR 功能描述:FTG for Intel㈢ Pentium㈢ 4 CPU and Chipsets |

| CY28349B | 制造商:SPECTRALINEAR 制造商全稱:SPECTRALINEAR 功能描述:FTG for Intel㈢ Pentium㈢ 4 CPU and Chipsets |

| CY28349B_05 | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:FTG for Intel㈢ Pentium㈢ 4 CPU and Chipsets |

| CY28349BOC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY28349BOCT | 制造商:Rochester Electronics LLC 功能描述:FTG FOR INTEL 830M AND 845 CHIPSETS (CK-408) - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。