- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378985 > CXD2728Q (Sony Corporation) Single-Chip Dolby Pro Logic Surround Decoder(單片杜比環(huán)繞Pro邏輯解碼器) PDF資料下載

參數(shù)資料

| 型號(hào): | CXD2728Q |

| 廠商: | Sony Corporation |

| 英文描述: | Single-Chip Dolby Pro Logic Surround Decoder(單片杜比環(huán)繞Pro邏輯解碼器) |

| 中文描述: | 單片杜比定向邏輯環(huán)繞聲解碼器(單片杜比環(huán)繞專業(yè)邏輯解碼器) |

| 文件頁數(shù): | 18/61頁 |

| 文件大小: | 467K |

| 代理商: | CXD2728Q |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當(dāng)前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁

– 18 –

CXD2728Q

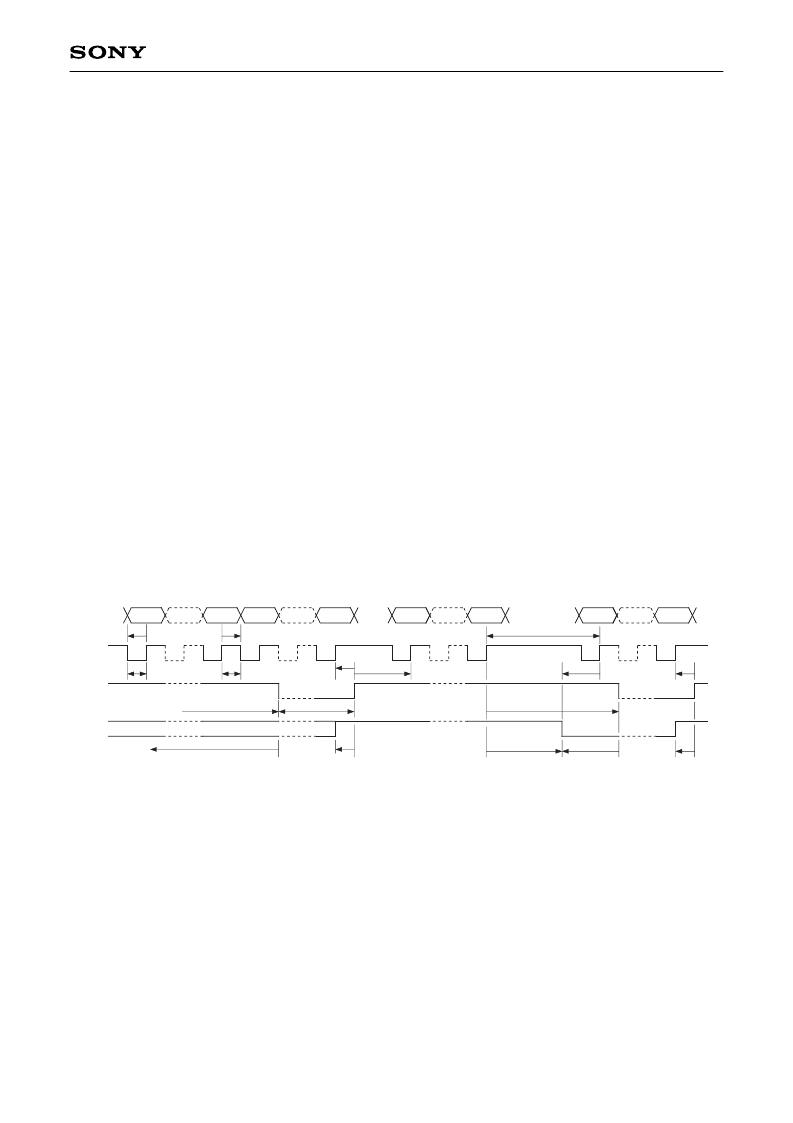

(4) Details of Communication Methods

The definitions of signal timing required for control from the microcomputer are given below.

(4)-1. Signal Timing

First, address section data and mode section data are sent from the microcomputer, synchronized to SCK, to

the RVDT pin.

The address section data is 8 bits for both the coefficient RAM and setup register, and the setup register has a

length of one word, so optional data can be transferred. Address section data is sent with LSB first.

Mode section data is fixed at 8 bits regardless of the transfer contents.

The phase relationship between SCK and RV data (data applied to the RVDT pin) has the following

restrictions:

RV data must be established before SCK rises (t

DS

≥

20ns).

RV data must be held for 1t + 20ns or more after SCK rises (t

DH

).

SCK itself has the following restrictions:

SCK Low level must be 1t + 20ns or more (t

SWL

).

SCK High level must be 1t + 20ns or more (t

SWH

).

After the SCK rise which corresponds to the mode section final data, XLAT rises (t

SLP

≥

20ns).

The XLAT Low level width must be maintained at 1t + 20ns or more (t

LWL

). The fall timing is restricted in that

even if REDY falls due to SCK during the preceding transfer, 3t + 20ns or more (t

SLD

) is required from the SCK

rise which corresponds to the data section final data.

Further, if preceding transfers have been performed and REDY = Low, XLAT must rise after REDY = High.

A0

A7

M0

M7

SQ00

SQ15

RVDT

SCK

XLAT

REDY

A0

M7

t

DH

t

DS

t

SWH

t

SWL

t

SLD

or t

LWH

t

LWL

t

RLP

t

LDR

t

LSD

t

SLP

t

BSP

t

SLP

t

LDR

t

RLP

t

SS

t

SLD

t

SBD

D0/SQ00

D15/SQ15

Fig. 5-2. Write Timing

t is the cycle of 2/3 the clock frequency applied to the XTLI pin. (512fs)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CXD2930BR | GPS LSI With Built-In 32-Bit RISC CPU(全球定位系統(tǒng)(GPS)大規(guī)模集成電路(LSI)(內(nèi)置32位RISC中央處理器)) |

| CXD2931R | 1 Chip GPS LSI(單片全球定位系統(tǒng)(GPS)大規(guī)模集成電路LSI) |

| CXD2951GA-2 | Single Chip GPS LSI |

| CXD3000R | CD Digital Signal Processor with Built-in Digital Servo and DAC |

| CXD3005R | CD Digital Signal Processor with Built-in Digital Servo and DAC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CXD2917 | 制造商:SONY 制造商全稱:Sony Corporation 功能描述:DIGITAL AUDIO DATA MODULATION AND TRANSMISSION |

| CXD2917Q | 制造商:SONY 制造商全稱:Sony Corporation 功能描述:DIGITAL AUDIO DATA MODULATION AND TRANSMISSION |

| CXD2930BR | 制造商:SONY 制造商全稱:Sony Corporation 功能描述:GPS LSI with Built-in 32-bit RISC CPU |

| CXD2931GA-9 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:RF/BASEBAND CIRCUIT|CMOS|LGA|144PIN|CERAMIC |

| CXD2931R | 制造商:SONY 制造商全稱:Sony Corporation 功能描述:1 chip GPS LSI |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。