- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369674 > CT2555-FP (Aeroflex Inc.) CT2553 / 2554 / 2555 / 2556 Advanced Integrated MUX (AIM) Hybrid FOR MIL-STD-1553 PDF資料下載

參數(shù)資料

| 型號: | CT2555-FP |

| 廠商: | Aeroflex Inc. |

| 英文描述: | CT2553 / 2554 / 2555 / 2556 Advanced Integrated MUX (AIM) Hybrid FOR MIL-STD-1553 |

| 中文描述: | CT2553 / 2554 /二千五百五十六分之二千五百五十五高級集成復(fù)用器(AIM)的混合的MIL - STD - 1553的 |

| 文件頁數(shù): | 32/36頁 |

| 文件大小: | 352K |

| 代理商: | CT2555-FP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁第35頁第36頁

Aeroflex Circuit Technology

32

SCDCT2553 REV B 8/6/99 Plainview NY (516) 694-6700

45

46

47

48

49

50

51

52

53

54

55

D09

D11

D13

D15

RTAD3

RTAD2

RTADP

SA/MC-2

SA/MC-4

SA/MC-3

THIS-RT

(5)

(5)

(5)

(5)

(5)

(5)

(5)

-

-

-

-

-0.4

-0.4

-0.4

-0.4

-0.4

-0.4

-0.4

-

-

-

-

-400

-400

-400

-400

-

-

-

-400

-400

-400

-400

3.6

3.6

3.6

3.6

-

-

-

2.0

2.0

2.0

2.0

I/O Data Bus Bit 9.

I/O Data Bus Bit 11.

I/O Data Bus Bit 13.

I/O Data Bus Bit 15 (MSB).

Remote Terminal Address Bit 3.

Remote Terminal Address Bit 2.

Remote Terminal Address Parity input.

Subaddress/Mode Command Bit 2. B8 (MSB) counter.

Subaddress/Mode Command Bit 4.

Subaddress/Mode Command Bit 3.

Logic 0 pulse indicates receipt of a valid command word which contains

the Remote Terminal address equivalent to the RTADO-RTAD4 inputs.

RTU (address) Parity Error. Logic 0 indicates RTU address parity (odd

parity: RTADO-RTAD4, RTADP) has been violated.

Transmit/Receive 1553 data. Latched T/R bit from current command

word.

+5V power supply connection for the B channel transceiver.

Transmit/Receive transceiver-B. Inverted I/O to coupling transformer

that connects to channel B of the 1553 Bus.

Address Bit 0 (LSB).

Address Bit 2.

Address Bit 4.

Address Bit 6.

Address Bit 8.

Address Bit 10.

Address Bit 12.

Address Bit 14.

Memory Write. Output pulse to write data into memory.

Memory Enable In. Enables internal RAM only; connect directly to

MEMENA-OUT.

In Command. Indicates BC or RTU currently in message transfer

sequence.

Master Clear. Power-on reset from CPU.

Interrupt. Interrupt pulse line to CPU.

Input/Output Enable. Output to enable external hybrid to the

address/data bus.

Select. Input from the CPU. When active, selects CT2553 for operation.

Ready Data. When active indicates data has been received from, or is

available to, the CPU.

Tag Enable. Enables an external time to counter for transferring the

time tag word into memory.

+5V input/power supply for channel A transceiver.

Transmit/Receive transceiver-A. Inverted I/O to the coupling

transformer that connects

to the A channel of the 1553 Bus.

56

RTPARERR

-

-

-400

2.0

57

T/R

-

-

-400

2.0

58

59

+5VB

TX/RX-B

-

-

-

-

-

-

-

-

60

61

62

63

64

65

66

67

68

69

A00

A02

A04

A06

A08

A10

A12

A14

MEMWR

MEMENA-IN

(5)

(5)

(5)

(5)

(5)

(5)

(5)

(5)

-

±20

-0.4

-0.4

-0.4

-0.4

-0.4

-0.4

-0.4

-0.4

-

±0.02

-400

-400

-400

-400

-400

-400

-400

-400

-400

-

3.6

3.6

3.6

3.6

3.6

3.6

3.6

3.6

4.0

-

70

INCMD

-

-

-400

2.0

71

72

73

MSTRCLR

INT

IOEN

(6)

-

-

-0.7

-

-

-

-

-400

-400

4.0

4.0

74

75

SELECT

READYD

(6)

-

-0.7

-

-

-

-400

4.0

76

TAGEN

-

-

-400

4.0

77

78

+5VA

TX/RX-A

-

-

-

-

-

-

-

-

1. I

IH

is specified at: V

CC

= 5.5V, V

IH

= 2.7V.

2. I

IL

is specified at: V

CC

= 5.5V, V

IL

= 0.4V.

3. I

OH

is specified at: V

CC

= 4.5V, V

IH

= 2.4V.

4. I

OL

is specified at: V

CC

= 4.5V, V

IH

= 0.4V.

5. Internal Pull-up Resistor = 30K Ohms, typ.

6. Internal Pull-up Resistor = 16K Ohms, typ.

7. Pin 13 = B6, Pin 15 = B7 and Pin 52 = B8 (MSB). B6, B7 and B8 are the MSB lines of an 8 BIT Counter used in the BC and MT

mode to count 32 WORD TRANSFERS to memory (16 words received off the bus) for a total of 128 DATA and Tag words (in

MT mode). (See pages 19 & 20 for discussion.)

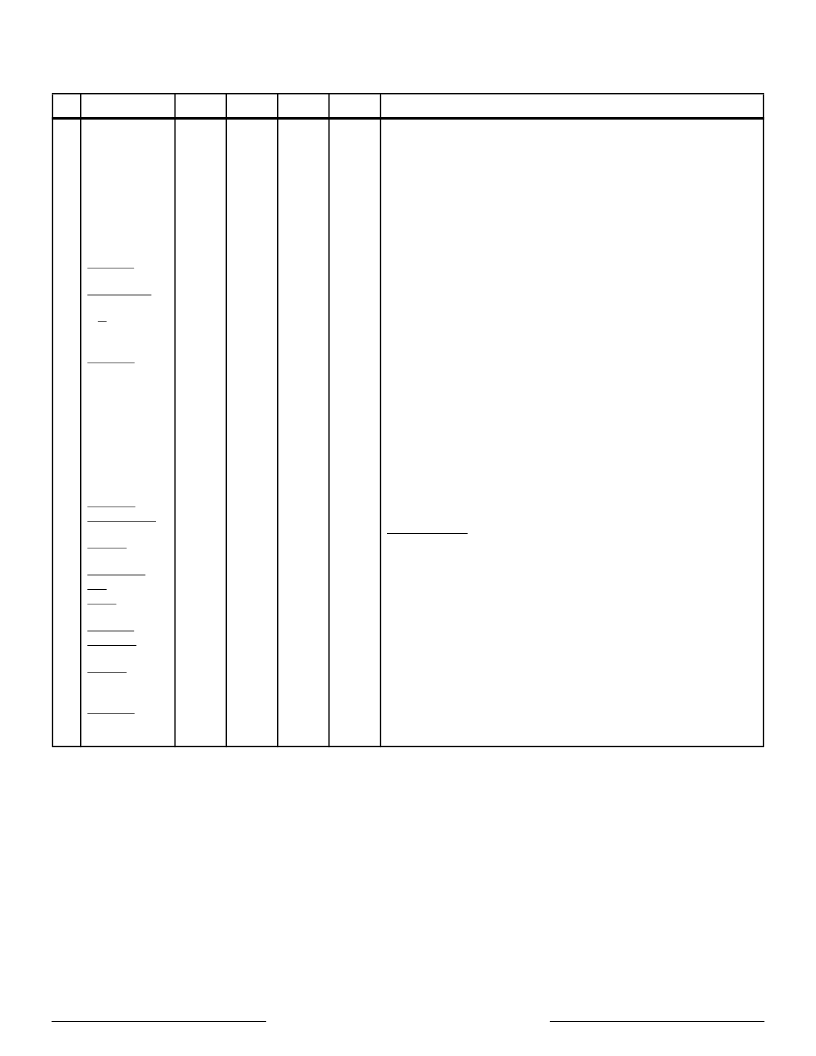

Table 7A – CT2553 Pin Function Table (78 Pin DIP) (continued)

Pin

Name

I

IH

(μA)

I

IL

(mA) I

OH

(μA) I

OL

(mA)

Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CT2553 | CT2553 / 2554 / 2555 / 2556 Advanced Integrated MUX (AIM) Hybrid FOR MIL-STD-1553 |

| CT2554 | CT2553 / 2554 / 2555 / 2556 Advanced Integrated MUX (AIM) Hybrid FOR MIL-STD-1553 |

| CT2555 | CT2553 / 2554 / 2555 / 2556 Advanced Integrated MUX (AIM) Hybrid FOR MIL-STD-1553 |

| CT2553-FP | CT2553 / 2554 / 2555 / 2556 Advanced Integrated MUX (AIM) Hybrid FOR MIL-STD-1553 |

| CT2556 | CT2553 / 2554 / 2555 / 2556 Advanced Integrated MUX (AIM) Hybrid FOR MIL-STD-1553 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CT2556 | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:CT2553 / 2554 / 2555 / 2556 Advanced Integrated MUX (AIM) Hybrid FOR MIL-STD-1553 |

| CT2556-FP | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:CT2553 / 2554 / 2555 / 2556 Advanced Integrated MUX (AIM) Hybrid FOR MIL-STD-1553 |

| CT2561 | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:CT2561 Bus Controller, Remote Terminal and BUS Monitor FOR MIL-STD-1553B |

| CT2561-FP | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:CT2561 Bus Controller, Remote Terminal and BUS Monitor FOR MIL-STD-1553B |

| CT2565 | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:CT2565 Bus Controller, Remote Terminal and BUS Monitor FOR MIL-STD-1553B |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。