- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄4068 > CS80C286-16 (Intersil)IC CPU 16BIT 5V 16MHZ 68-PLCC PDF資料下載

參數(shù)資料

| 型號(hào): | CS80C286-16 |

| 廠商: | Intersil |

| 文件頁(yè)數(shù): | 5/60頁(yè) |

| 文件大小: | 0K |

| 描述: | IC CPU 16BIT 5V 16MHZ 68-PLCC |

| 標(biāo)準(zhǔn)包裝: | 126 |

| 處理器類(lèi)型: | 80C286 16-位 |

| 速度: | 16MHz |

| 電壓: | 5V |

| 安裝類(lèi)型: | 表面貼裝 |

| 封裝/外殼: | 68-LCC(J 形引線) |

| 供應(yīng)商設(shè)備封裝: | 68-PLCC(24.23x24.23) |

| 包裝: | 管件 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)

13

I/O Space

The I/O space consists of 64K 8-bit ports, 32K 16-bit ports, or

a combination of the two. I/O instructions address the I/O

space with either an 8-bit port address, specified in the

instruction, or a 16-bit port address in the DX register. 8-bit

port addresses are zero extended such that A15-A8 are LOW.

I/O port addresses 00F8(H) through 00FF(H) are reserved.

Interrupts

An interrupt transfers execution to a new program location.

The old program address (CS:lP) and machine state (Flags)

are saved on the stack to allow resumption of the interrupted

program. Interrupts fall into three classes: hardware initiated,

INT instructions, and instruction exceptions. Hardware initi-

ated interrupts occur in response to an external input and

are classified as non-maskable or maskable. Programs may

cause an interrupt with an INT instruction. Instruction excep-

tions occur when an unusual condition which prevents fur-

ther instruction processing is detected while attempting to

execute an instruction. The return address from an excep-

tion will always point to the instruction causing the exception

and include any leading instruction prefixes.

A table containing up to 256 pointers defines the proper

interrupt service routine for each interrupt. Interrupts 0-31,

some of which are used for instruction exceptions, are

reserved. For each interrupt, an 8-bit vector must be sup-

plied to the 80C286 which identifies the appropriate table

entry. Exceptions supply the interrupt vector internally. INT

instructions contain or imply the vector and allow access to

all 256 interrupts. Maskable hardware initiated interrupts

supply the 8-bit vector to the CPU during an interrupt

acknowledge bus sequence. Nonmaskable hardware inter-

rupts use a predefined internally supplied vector.

Maskable Interrupt (INTR)

The 80C286 provides a maskable hardware interrupt request

pin, INTR. Software enables this input by setting the interrupt

flag bit (IF) in the flag word. All 224 user-defined interrupt

sources can share this input, yet they can retain separate

interrupt handlers. An 8-bit vector read by the CPU during the

interrupt acknowledge sequence (discussed in System Inter-

face section) identifies the source of the interrupt.

The processor automatically disables further maskable inter-

rupts internally by resetting the IF as part of the response to

an interrupt or exception. The saved flag word will reflect the

enable status of the processor prior to the interrupt. Until the

flag word is restored to the flag register, the interrupt flag will

be zero unless specifically set. The interrupt return instruc-

tion includes restoring the flag word, thereby restoring the

original status of IF.

Non-Maskable Interrupt Request (NMI)

A non-maskable interrupt input (NMI) is also provided. NMI

has higher priority than INTR. A typical use of NMI would be

to activate a power failure routine. The activation of this input

causes an interrupt with an internally supplied vector value

of 2. No external interrupt acknowledge sequence is per-

formed.

While executing the NMI servicing procedure, the 80C286

will service neither further NMI requests, INTR requests, nor

the processor extension segment overrun interrupt until an

interrupt return (lRET) instruction is executed or the CPU is

reset. If NMI occurs while currently servicing an NMI, its

presence will be saved for servicing after executing the first

IRET instruction. IF is cleared at the beginning of an NMI

interrupt to inhibit INTR interrupts.

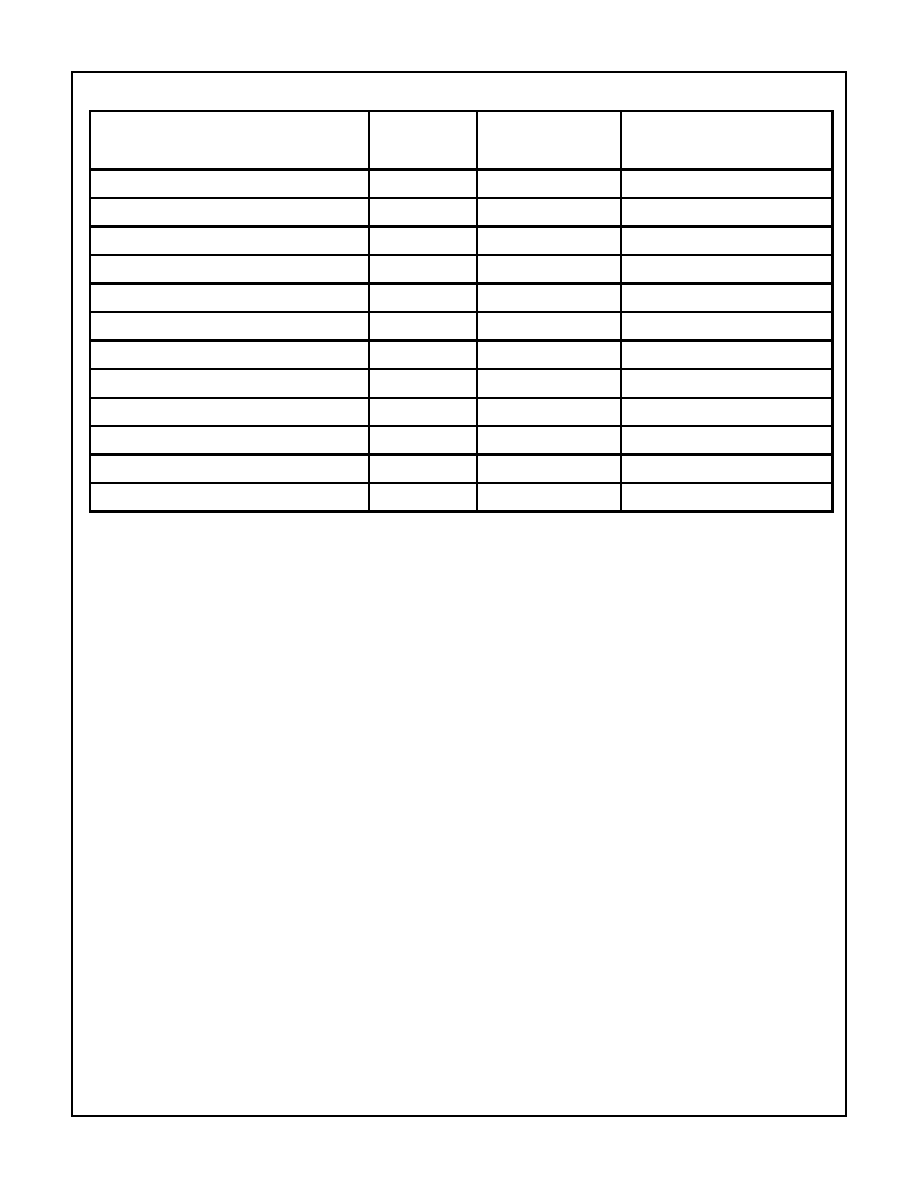

TABLE 4. INTERRUPT VECTOR ASSIGNMENTS

FUNCTION

INTERRUPT

NUMBER

RELATED

INSTRUCTIONS

DOES RETURN ADDRESS

POINT TO INSTRUCTION

CAUSING EXCEPTION?

Divide Error Exception

0

DlV, lDlV

Yes

Single Step Interrupt

1

All

NMI Interrupt

2

INT 2 or NMI Pin

Breakpoint Interrupt

3

INT 3

INTO Detected Overflow Exception

4

INTO

No

BOUND Range Exceeded Exception

s

BOUND

Yes

Invalid Opcode Exception

6

Any Undefined Opcode

Yes

Processor Extension Not Available Exception

7

ESC or WAIT

Yes

Reserved - Do Not Use

8 - 15

Processor Extension Error Interrupt

16

ESC or WAIT

Reserved

17 - 31

User Defined

32 - 255

80C286

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ACB90DHAR | CONN EDGECARD 180PS R/A .050 DIP |

| MPC857TZQ66B | IC MPU PWRQUICC 66MHZ 357-PBGA |

| ABB95DHAS | CONN EDGECARD 190PS R/A .050 SLD |

| MPC857TVR66B | IC MPU POWERQUICC 66MHZ 357-PBGA |

| MPC8271ZQTIEA | IC MPU POWERQUICC II 516-PBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CS80C286-1696 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS80C286-2 | 制造商:Harris Corporation 功能描述: |

| CS80C286-20 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS80C286-2096 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS80C286-20S2463 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。