- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366749 > CAT64LC40UATE13 72-Mbit(2M x 36/4M x 18/1M x 72) Pipelined SRAM with NoBL™ Architecture PDF資料下載

參數(shù)資料

| 型號(hào): | CAT64LC40UATE13 |

| 英文描述: | 72-Mbit(2M x 36/4M x 18/1M x 72) Pipelined SRAM with NoBL™ Architecture |

| 中文描述: | EEPROM的 |

| 文件頁(yè)數(shù): | 2/11頁(yè) |

| 文件大小: | 140K |

| 代理商: | CAT64LC40UATE13 |

2

CAT64LC10/20/40

Doc. No. 1021, Rev. A

ABSOLUTE MAXIMUM RATINGS*

Temperature Under Bias ................. –55

°

C to +125

°

C

Storage Temperature....................... –65

°

C to +150

°

C

Voltage on any Pin with

Respect to Ground

(1)

............ –2.0V to +V

CC

+2.0V

V

CC

with Respect to Ground ............... –2.0V to +7.0V

Package Power Dissipation

Capability (Ta = 25

°

C)................................... 1.0W

Lead Soldering Temperature (10 secs) ............ 300

°

C

Output Short Circuit Current

(2)

........................ 100 mA

*COMMENT

Stresses above those listed under “Absolute Maximum

Ratings” may cause permanent damage to the device.

These are stress ratings only, and functional operation of

the device at these or any other conditions outside of those

listed in the operational sections of this specification is not

implied. Exposure to any absolute maximum rating for

extended periods may affect device performance and

reliability.

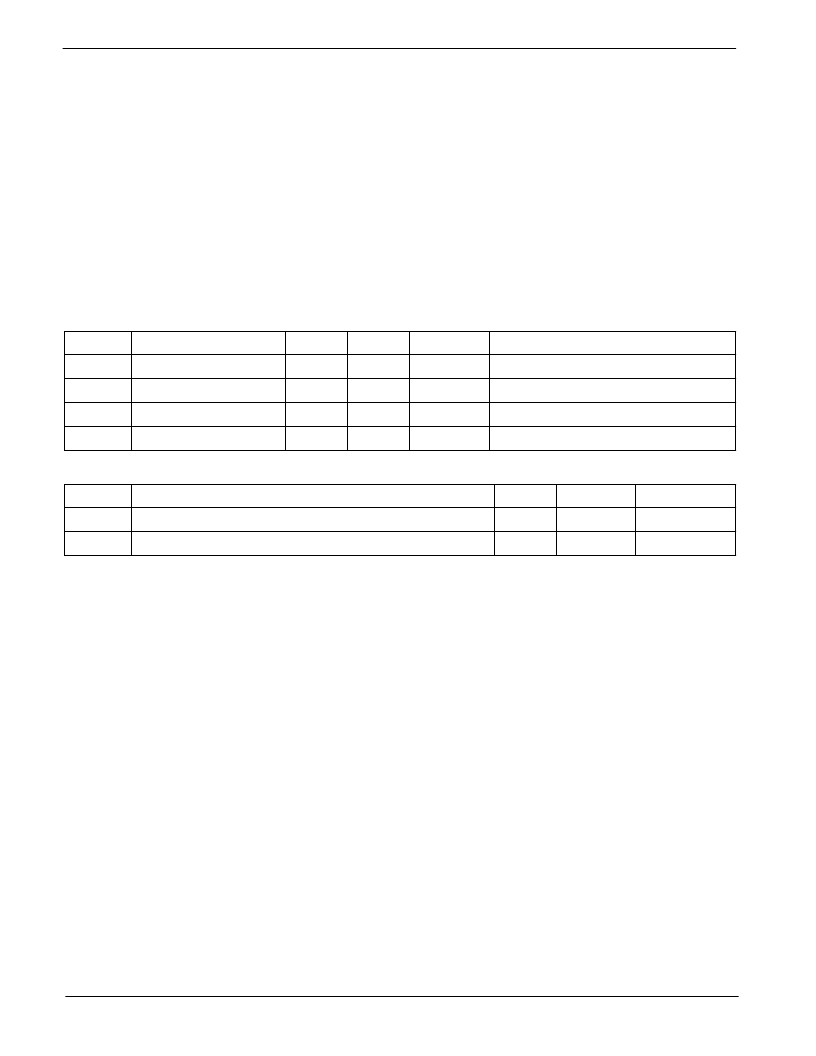

RELIABILITY CHARACTERISTICS

Symbol

N

END(3)

Parameter

Min.

Max.

Units

Reference Test Method

Endurance

1,000,000

Cycles/Byte

MIL-STD-883, Test Method 1033

T

DR(3)

Data Retention

100

Years

MIL-STD-883, Test Method 1008

V

ZAP(3)

ESD Susceptibility

2000

Volts

MIL-STD-883, Test Method 3015

I

LTH(3)(4)

Latch-Up

100

mA

JEDEC Standard 17

CAPACITANCE

(T

A

= 25

°

C, f= 1.0 MHz, V

CC

=6.0V)

Symbol

C

I/O(3)

Input/Output Capacitance (DO, RDY/

BSY

)

Test

Max.

Units

Conditions

8

pF

V

I/O

= 0V

C

IN(3)

Input Capacitance (

CS

, SK, DI, RESET)

6

pF

V

IN

= 0V

Note:

(1) The minimum DC input voltage is –0.5V. During transitions, inputs may undershoot to –2.0V for periods of less than 20 ns. Maximum DC

voltage on output pins is V

CC

+0.5V, which may overshoot to V

CC

+2.0V for periods of less than 20 ns.

(2) Output shorted for no more than one second. No more than one output shorted at a time.

(3) This parameter is tested initially and after a design or process change that affects the parameter.

(4) Latch-up protection is provided for stresses up to 100 mA on address and data pins from –1V to V

CC

+1V.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CAT64LC40UITE13 | 72-Mbit(2M x 36/4M x 18/1M x 72) Pipelined SRAM with NoBL™ Architecture |

| CAT64LC40URATE13 | 72-Mbit (2M x 36/4M x 18/1M x 72) Pipelined Sync SRAM |

| CAT64LC40URITE13 | EEPROM |

| CAT64LC40URTE13 | EEPROM |

| CAT64LC40UTE13 | 72-Mbit QDR™-II SRAM 2-Word Burst Architecture |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CAT64LC40U-GT3 | 制造商:ONSEMI 制造商全稱:ON Semiconductor 功能描述:4 kb SPI Serial EEPROM |

| CAT64LC40UI-GT3 | 制造商:ONSEMI 制造商全稱:ON Semiconductor 功能描述:4 kb SPI Serial EEPROM |

| CAT64LC40UI-T3 | 制造商:ONSEMI 制造商全稱:ON Semiconductor 功能描述:4 kb SPI Serial EEPROM |

| CAT64LC40UITE13 | 制造商:CATALYST 制造商全稱:Catalyst Semiconductor 功能描述:1K/2K/4K-Bit SPI Serial E2PROM |

| CAT64LC40URATE13 | 制造商:CATALYST 制造商全稱:Catalyst Semiconductor 功能描述:1K/2K/4K-Bit SPI Serial E2PROM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。