- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄166632 > BU-65863F3-220 (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 PDF資料下載

參數(shù)資料

| 型號(hào): | BU-65863F3-220 |

| 廠商: | DATA DEVICE CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 |

| 封裝: | 0.880 INCH, CERAMIC, QFP-80 |

| 文件頁數(shù): | 24/75頁 |

| 文件大小: | 532K |

| 代理商: | BU-65863F3-220 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當(dāng)前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁

30

Data Device Corporation

www.ddc-web.com

BU-65743/65843/65863/65864

D-06/04-0

General Purpose Queue. The PCI Mini-ACE Mark3/Micro-ACE

TE BC allows for the creation of a general purpose queue. This

data structure provides a means for the message sequence

processor to convey information to the BC host. The BC op

code repertoire provides mechanisms to push various items on

this queue. These include the contents of the Time Tag

Register, the Block Status Word for the most recent message,

an immediate data value, or the contents of a specified memo-

ry address.

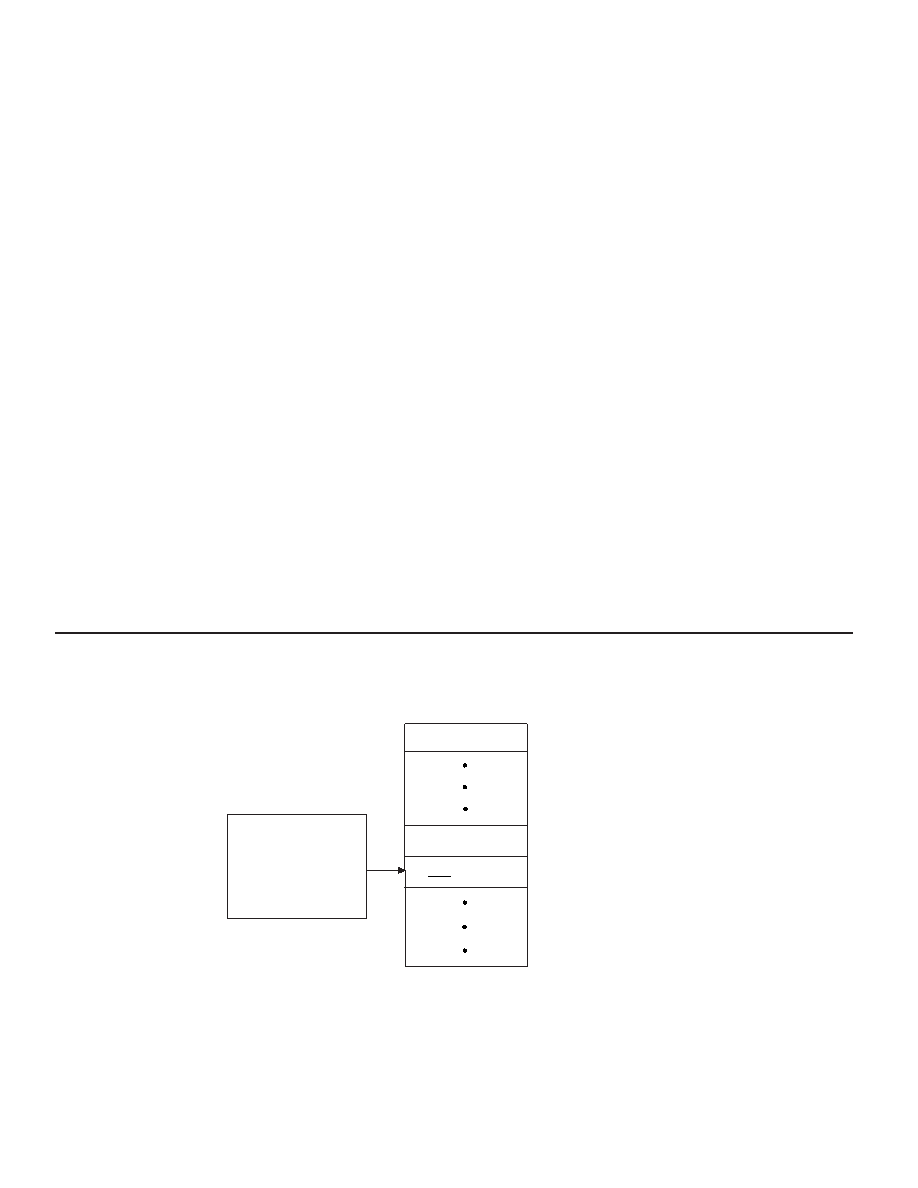

FIGURE 5 illustrates the operation of the BC General Purpose

Queue. Note that the BC General Purpose Queue Pointer

Register will always point to the next address location (modulo

64); that is, the location following the last location written by the

BC message sequence control engine.

If enabled, a BC GENERAL PURPOSE QUEUE ROLLOVER

interrupt will be issued when the value of the queue pointer

address rolls over at a 64-word boundary. The rollover will always

occur at a modulo 64 address.

REMOTE TERMINAL (RT) ARCHITECTURE

The PCI Mini-ACE Mark3/Micro-ACE TE's RT architecture builds

upon that of the ACE and Mini-ACE. The PCI Mini-ACE

Mark3/Micro-ACE TE provides multiprotocol support, with full

compliance to all of the commonly used data bus standards,

including MIL-STD-1553A, MIL-STD-1553B Notice 2, STANAG

3838, General Dynamics 16PP303, and McAirA3818, A5232,

and A5690. For the PCI Mini-ACE Mark3/Micro-ACE TE RT

mode, there is programmable flexibility enabling the RT to be con-

figured to fulfill any set of system requirements. This includes the

capability to meet the MIL-STD-1553A response time require-

ment of 2 to 5 s, and multiple options for mode code subad-

dresses, mode codes, RT status word, and RT BIT word.

The PCI Mini-ACE Mark3/Micro-ACE TE RT protocol design

implements all of the MIL-STD-1553B message formats and dual

redundant mode codes. The design has passed validation testing

for MIL-STD-1553B compliance. The PCI Mini-ACE Mark3/Micro-

ACE TE RT performs comprehensive error checking including

word and format validation, and checks for various RT-to-RT

transfer errors. One of the main features of the PCI Mini-ACE

Mark3/Micro-ACE TE RT is its choice of memory management

options. These include single buffering by subaddress, double

buffering for individual receive subaddresses, circular buffering by

individual subaddresses, and global circular buffering for multiple

(or all) subaddresses.

Other features of the PCI Mini-ACE Mark3/Micro-ACE TE RT

include a set of interrupt conditions, an interrupt status queue with

filtering based on valid and/or invalid messages, internal com-

mand illegalization, programmable busy by subaddress, multiple

options on time tagging.

LAST LOCATION

BC GENERAL

PURPOSE QUEUE

(64 Locations)

BC GENERAL

PURPOSE QUEUE

POINTER

REGISTER

NEXT LOCATION

FIGURE 5. BC GENERAL PURPOSE QUEUE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BU-65843B3-E02 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA324 |

| BU-65863B8-E02 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA324 |

| BU-65843B8-E02 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA324 |

| BU1003 | POWER TRANSISTOR |

| BU2003 | POWER TRANSISTOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BU-65-9 | 功能描述:測(cè)試電夾 HEAVY DUTY LARGE JAW GATOR CLIP WHITE RoHS:否 制造商:Pomona Electronics 類型:Minigrabber clip 顏色:Black |

| BU6650NUX | 制造商:ROHM 制造商全稱:Rohm 功能描述:3ch CMOS LDO Regulators |

| BU6650NUX_11 | 制造商:ROHM 制造商全稱:Rohm 功能描述:3ch CMOS LDO Regulators |

| BU6650NUX-TR | 功能描述:低壓差穩(wěn)壓器 - LDO LDO REG 0.2A 8PIN 2.8V 2.8V 1.8V RoHS:否 制造商:Texas Instruments 最大輸入電壓:36 V 輸出電壓:1.4 V to 20.5 V 回動(dòng)電壓(最大值):307 mV 輸出電流:1 A 負(fù)載調(diào)節(jié):0.3 % 輸出端數(shù)量: 輸出類型:Fixed 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-20 |

| BU6651NUX | 制造商:ROHM 制造商全稱:Rohm 功能描述:High-speed Load Response Full CMOS LDP Regulators |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。