- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄42903 > ATF-521P8-TR2G (AGILENT TECHNOLOGIES INC) C BAND, Si, N-CHANNEL, RF SMALL SIGNAL, HEMFET, MO-229 PDF資料下載

參數(shù)資料

| 型號: | ATF-521P8-TR2G |

| 廠商: | AGILENT TECHNOLOGIES INC |

| 元件分類: | 小信號晶體管 |

| 英文描述: | C BAND, Si, N-CHANNEL, RF SMALL SIGNAL, HEMFET, MO-229 |

| 封裝: | 2 X 2 MM, 0.75 MM HEIGHT, LPCC-8 |

| 文件頁數(shù): | 18/24頁 |

| 文件大?。?/td> | 248K |

| 代理商: | ATF-521P8-TR2G |

3

ATF-521P8 Electrical Specifications

TA = 25°C, DC bias for RF parameters is Vds = 4.5V and Ids = 200 mA unless otherwise specified.

Symbol

Parameter and Test Condition

Units

Min.

Typ.

Max.

Vgs

Operational Gate Voltage

Vds = 4.5V, Ids = 200 mA

V

—

0.62

—

Vth

Threshold Voltage

Vds = 4.5V, Ids = 16 mA

V

—

0.28

—

Idss

Saturated Drain Current

Vds = 4.5V, Vgs = 0V

A

—

14.8

—

Gm

Transconductance

Vds = 4.5V, Gm =

Idss/Vgs;

mmho

—

1300

—

Vgs = Vgs1 - Vgs2

Vgs1 = 0.55V, Vgs2 = 0.5V

Igss

Gate Leakage Current

Vds = 0V, Vgs = -4V

A

-20

0.49

—

NF

Noise Figure[1]

f = 2 GHz

dB

—

1.5

—

f = 900 MHz

dB

—

1.2

—

G

Gain [1]

f = 2 GHz

dB

15.5

17

18.5

f = 900 MHz

dB

—

17.2

—

OIP3

Output 3rd Order

f = 2 GHz

dBm

38.5

42

—

Intercept Point[1]

f = 900 MHz

dBm

—

42.5

—

P1dB

Output 1dB

f = 2 GHz

dBm

25

26.5

—

Compressed[1]

f = 900 MHz

dBm

—

26.5

—

PAE

Power Added Efficiency

f = 2 GHz

%

45

60

—

f = 900 MHz

%

—

56

—

ACLR

Adjacent Channel Leakage

Offset BW = 5 MHz

dBc

—

-51.4

—

Power Ratio[1,2]

Offset BW = 10 MHz

dBc

—

-61.5

—

Notes:

1. Measurements obtained using production test board described in Figure 6.

2. ACLR test spec is based on 3GPP TS 25.141 V5.3.1 (2002-06)

– Test Model 1

– Active Channels: PCCPCH + SCH + CPICH + PICH + SCCPCH + 64 DPCH (SF=128)

– Freq = 2140 MHz

– Pin = -5 dBm

– Chan Integ Bw = 3.84 MHz

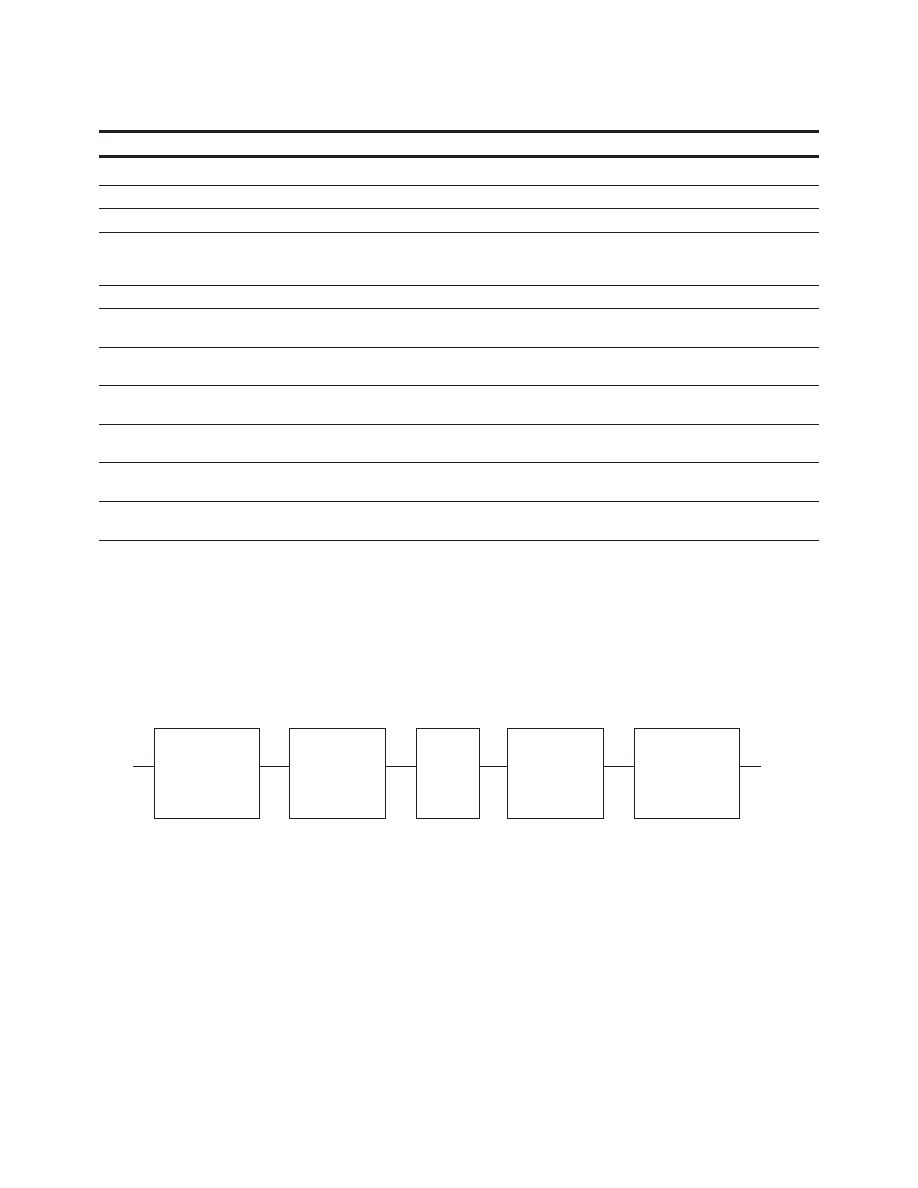

Input

50 Ohm

Transmission

Line Including

Gate Bias T

(0.3 dB loss)

Input

Matching Circuit

Γ_mag = 0.55

Γ_ang = -166°

(1.1 dB loss)

Output

Matching Circuit

Γ_mag = 0.35

Γ_ang = 168°

(0.9 dB loss)

DUT

50 Ohm

Transmission

Line and

Drain Bias T

(0.3 dB loss)

Output

Figure 6. Block diagram of the 2 GHz production test board used for NF, Gain, OIP3 , P1dB and PAE and ACLR measurements. This circuit achieves a

trade-off between optimal OIP3, P1dB and VSWR. Circuit losses have been de-embedded from actual measurements.

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。