- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366557 > AMD-K6 (Advanced Micro Devices, Inc.) Circular Connector; No. of Contacts:5; Series:MS27497; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:14; Circular Contact Gender:Pin; Circular Shell Style:Wall Mount Receptacle; Insert Arrangement:14-5 RoHS Compliant: No PDF資料下載

參數(shù)資料

| 型號: | AMD-K6 |

| 廠商: | Advanced Micro Devices, Inc. |

| 元件分類: | 圓形連接器 |

| 英文描述: | Circular Connector; No. of Contacts:5; Series:MS27497; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:14; Circular Contact Gender:Pin; Circular Shell Style:Wall Mount Receptacle; Insert Arrangement:14-5 RoHS Compliant: No |

| 中文描述: | 的AMD - K6處理器 |

| 文件頁數(shù): | 148/346頁 |

| 文件大小: | 4918K |

| 代理商: | AMD-K6 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁當前第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁第221頁第222頁第223頁第224頁第225頁第226頁第227頁第228頁第229頁第230頁第231頁第232頁第233頁第234頁第235頁第236頁第237頁第238頁第239頁第240頁第241頁第242頁第243頁第244頁第245頁第246頁第247頁第248頁第249頁第250頁第251頁第252頁第253頁第254頁第255頁第256頁第257頁第258頁第259頁第260頁第261頁第262頁第263頁第264頁第265頁第266頁第267頁第268頁第269頁第270頁第271頁第272頁第273頁第274頁第275頁第276頁第277頁第278頁第279頁第280頁第281頁第282頁第283頁第284頁第285頁第286頁第287頁第288頁第289頁第290頁第291頁第292頁第293頁第294頁第295頁第296頁第297頁第298頁第299頁第300頁第301頁第302頁第303頁第304頁第305頁第306頁第307頁第308頁第309頁第310頁第311頁第312頁第313頁第314頁第315頁第316頁第317頁第318頁第319頁第320頁第321頁第322頁第323頁第324頁第325頁第326頁第327頁第328頁第329頁第330頁第331頁第332頁第333頁第334頁第335頁第336頁第337頁第338頁第339頁第340頁第341頁第342頁第343頁第344頁第345頁第346頁

130

Bus Cycles

Chapter 6

AMD-K6

Processor Data Sheet

20695H/0—March 1998

Preliminary Information

Burst Reads and

Pipelined Burst Reads

Figure 47 on page 131 shows normal burst read cycles and a

pipelined burst read cycle. The AMD-K6 processor drives

CACHE# and ADS# together to specify that the current bus

cycle is a burst cycle. If the processor samples KEN# asserted

with the first BRDY#, it performs burst transfers. During the

burst transfers, the system logic must ignore BE[7:0]# and must

return all eight bytes beginning at the starting address the

processor asserts on A[31:3]. Depending on the starting

address, the system logic must determine the successive

quadword addresses (A[4:3]) for each transfer in a burst, as

shown in Table 21. The processor expects the second, third, and

fourth quadwords to occur in the sequences shown in Table 21.

In Figure 47, the processor drives CACHE# throughout all burst

read cycles. In the first burst read cycle, the processor drives

ADS# and CACHE#, then samples BRDY# on every clock edge

starting with the clock edge after the clock edge that negates

ADS#. The processor samples KEN# asserted on the clock edge

on which the first BRDY# is sampled asserted, executes a

32-byte burst read cycle, and expects to sample BRDY# a total

of four times. An ideal no-wait state access is shown in Figure

47, whereas most system logic solutions add wait states between

the transfers.

The second burst read cycle illustrates a similar sequence, but

the processor samples NA# asserted on the same clock edge

that the first BRDY# is sampled asserted. NA# assertion

indicates the system logic is requesting the processor to output

the next address early (also known as a pipeline transfer

request). Without waiting for the current cycle to complete, the

processor drives ADS# and related signals for the next burst

cycle. Pipelining can reduce CPU cycle-to-cycle idle times.

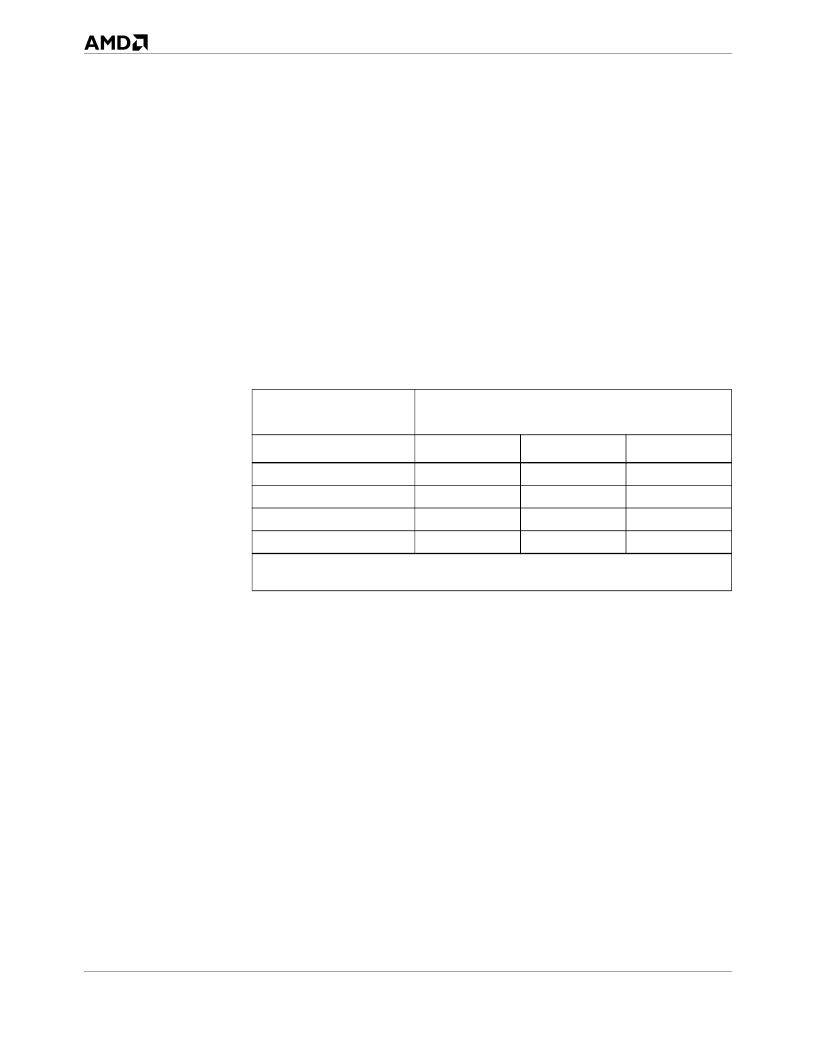

Table 21. A[4:3] Address-Generation Sequence During Bursts

Address Driven By

Processor on A[4:3]

A[4:3] Addresses of Subsequent

Quadwords* Generated By System Logic

Quadword 1

00b

01b

10b

11b

Quadword 2

01b

00b

11b

10b

Quadword 3

10b

11b

00b

01b

Quadword 4

11b

10b

01b

00b

Note:

*

quadword = 8 bytes

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AMD27C64-150PI | 64 Kilobit (8,192 x 8-Bit) CMOS EPROM |

| AMD27C64 | 64 Kilobit (8,192 x 8-Bit) CMOS EPROM |

| AMD27C64-120DC | 64 Kilobit (8,192 x 8-Bit) CMOS EPROM |

| AMD27C64-120DCB | 64 Kilobit (8,192 x 8-Bit) CMOS EPROM |

| AMD27C64-120DE | 64 Kilobit (8,192 x 8-Bit) CMOS EPROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AMD-K6/233ACZ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| AMD-K6/233BCZ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| AMD-K6/266ACZ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| AMD-K6/266BCZ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| AMD-K6/300ADZ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。