- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄366544 > AM50DL128BH85IT (Advanced Micro Devices, Inc.) CA-BAYONET PDF資料下載

參數(shù)資料

| 型號(hào): | AM50DL128BH85IT |

| 廠(chǎng)商: | Advanced Micro Devices, Inc. |

| 英文描述: | CA-BAYONET |

| 中文描述: | 堆疊式多芯片封裝(MCP)閃存和SRAM |

| 文件頁(yè)數(shù): | 59/68頁(yè) |

| 文件大小: | 959K |

| 代理商: | AM50DL128BH85IT |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)當(dāng)前第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)

October 7, 2003

Am50DL128BH

57

A D V A N C E I N F O R M A T I O N

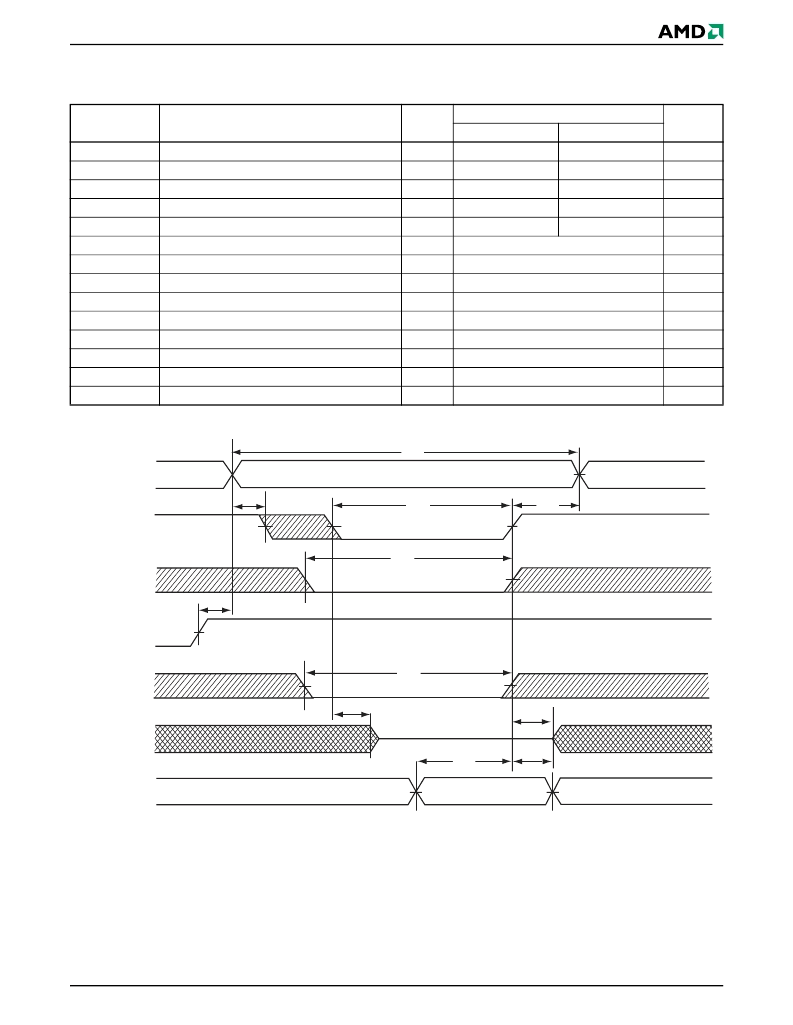

pSRAM AC CHARACTERISTICS

Write Cycle

Notes:

1. If the device is using the I/Os to output data, input signals of reverse polarity must not be applied.

2. If OE# is high during the write cycle, the outputs will remain at high impedance.

3. If CE#1ps, LB# or UB# goes low at the same time or after WE# goes low, the outputs will remain at high impedance.

4. If CE#1ps, LB# or UB# goes high at the same time or before WE# goes high, the outputs will remain at high impedance.

Figure 31.

Pseudo SRAM Write Cycle—WE# Control

Parameter

Symbol

Description

Speed

Unit

56, 70

85

t

WC

t

WP

t

CW

t

BW

t

AW

t

AS

t

WR

t

ODW

t

OEW

t

DS

t

DH

t

CH

t

CEH

t

WEH

Write Cycle Time

Min

70

85

ns

Write Pulse Time

Min

50

60

ns

Chip Enable to End of Write

Min

60

70

ns

Data Byte Control to End of Write

Min

60

70

ns

Address Valid to End of Write

Min

60

70

ns

Address Setup Time

Min

0

ns

Write Recovery Time

Min

0

ns

WE# Low to Write to Output High-Z

Max

20

ns

WE# High to Write to Output Active

Min

0

ns

Data Set-up Time

Min

30

Data Hold from Write Time

Min

0

ns

CE2 Hold Time

Min

300

μs

Chip Enable High Pulse Width

Min

10

ns

Write Enable High Pulse Width

Min

6

ns

t

WC

t

WP

t

WR

t

CW

t

BW

Valid Data In

t

AS

t

CH

t

OEW

Addresses

A20 to A0

WE#

CE#1s

CE2s

LB#, UB#

D

IN

DQ15 to DQ0

D

OUT

DQ15 to DQO

t

ODW

t

DS

t

DH

High-Z

(Note 1)

(Note 3)

(Note 4)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM50DL128BH | Circular Connector; No. of Contacts:128; Series:MS27505; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:25; Circular Contact Gender:Socket; Circular Shell Style:Box Mount Receptacle RoHS Compliant: No |

| AM50DL128BH56I | Circular Connector; No. of Contacts:56; Series:MS27505; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:25; Circular Contact Gender:Socket; Circular Shell Style:Box Mount Receptacle RoHS Compliant: No |

| AM50DL128BH56IS | Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

| AM50DL128BH56IT | Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

| AM50DL128BH70I | Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM50DL128CG | 制造商:SPANSION 制造商全稱(chēng):SPANSION 功能描述:Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

| AM50DL128CG70IS | 制造商:SPANSION 制造商全稱(chēng):SPANSION 功能描述:Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

| AM50DL128CG70IT | 制造商:SPANSION 制造商全稱(chēng):SPANSION 功能描述:Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

| AM50DL128CG85IS | 制造商:SPANSION 制造商全稱(chēng):SPANSION 功能描述:Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

| AM50DL128CG85IT | 制造商:SPANSION 制造商全稱(chēng):SPANSION 功能描述:Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。