- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366544 > AM49DL640BG30IS (Spansion Inc.) Stacked Multi-Chip Package (MCP) Flash Memory and SRAM PDF資料下載

參數(shù)資料

| 型號: | AM49DL640BG30IS |

| 廠商: | Spansion Inc. |

| 元件分類: | DRAM |

| 英文描述: | Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

| 中文描述: | 堆疊式多芯片封裝(MCP)閃存和SRAM |

| 文件頁數(shù): | 59/65頁 |

| 文件大?。?/td> | 1005K |

| 代理商: | AM49DL640BG30IS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁當(dāng)前第59頁第60頁第61頁第62頁第63頁第64頁第65頁

58

Am49DL640AG

April 1, 2003

P R E L I M I N A R Y

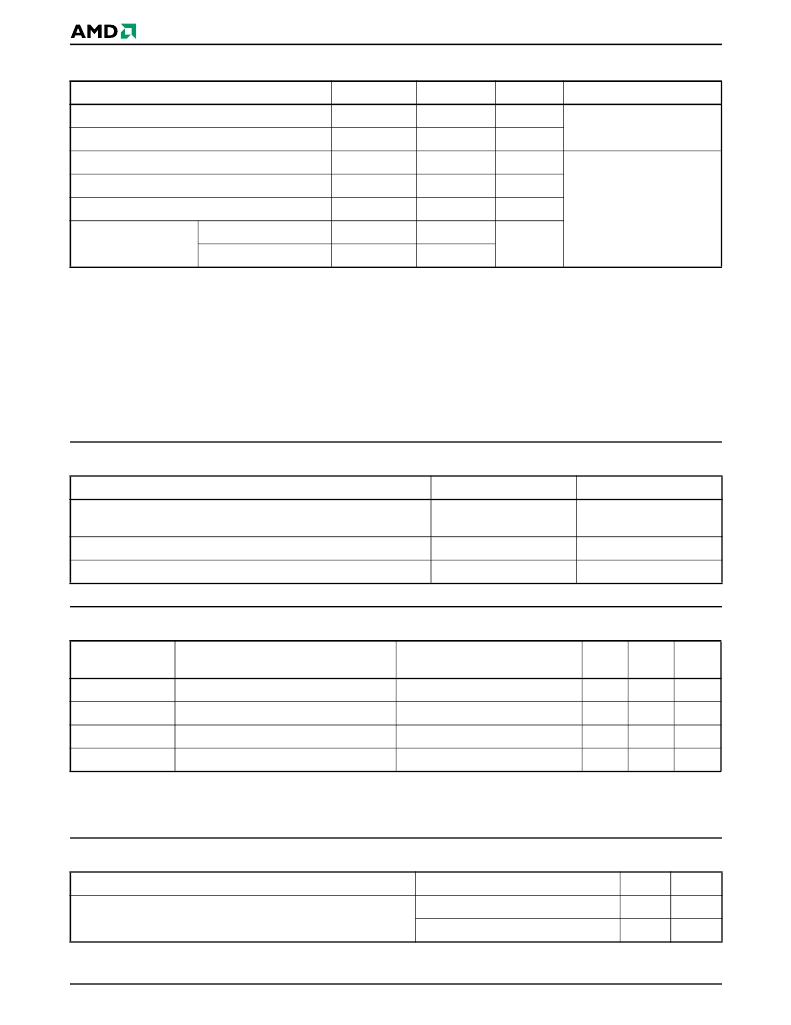

FLASH ERASE AND PROGRAMMING PERFORMANCE

Notes:

1. Typical program and erase times assume the following conditions: 25

°

C, 3.0 V V

CC

, 1,000,000 cycles. Additionally,

programming typicals assume checkerboard pattern.

2. Under worst case conditions of 90

°

C, V

CC

= 2.7 V, 1,000,000 cycles.

3. The typical chip programming time is considerably less than the maximum chip programming time listed, since most bytes

program faster than the maximum program times listed.

4. In the pre-programming step of the Embedded Erase algorithm, all bytes are programmed to 00h before erasure.

5. System-level overhead is the time required to execute the two- or four-bus-cycle sequence for the program command. See Table

12 for further information on command definitions.

6. The device has a minimum erase and program cycle endurance of 1,000,000 cycles.

LATCHUP CHARACTERISTICS

Note:

Includes all pins except V

CC

. Test conditions: V

CC

= 3.0 V, one pin at a time.

PACKAGE PIN CAPACITANCE

Notes:

1. Sampled, not 100% tested.

2. Test conditions T

A

= 25°C, f = 1.0 MHz.

FLASH DATA RETENTION

Parameter

Typ (Note 1)

Max (Note 2)

Unit

Comments

Sector Erase Time

0.4

5

sec

Excludes 00h programming

prior to erasure (Note 4)

Chip Erase Time

56

sec

Byte Program Time

5

150

μs

Excludes system level

overhead (Note 5)

Accelerated Byte/Word Program Time

4

120

μs

Word Program Time

7

210

μs

Chip Program Time

(Note 3)

Byte Mode

42

126

sec

Word Mode

28

84

Description

Min

Max

Input voltage with respect to V

SS

on all pins except I/O pins

(including A9, OE#, and RESET#)

–1.0 V

12.5 V

Input voltage with respect to V

SS

on all I/O pins

–1.0 V

V

CC

+ 1.0 V

V

CC

Current

–100 mA

+100 mA

Parameter

Symbol

Parameter Description

Test Setup

Typ

Max

Unit

C

IN

Input Capacitance

V

IN

= 0

11

14

pF

C

OUT

Output Capacitance

V

OUT

= 0

12

16

pF

C

IN2

Control Pin Capacitance

V

IN

= 0

14

16

pF

C

IN3

WP#/ACC Pin Capacitance

V

IN

= 0

17

20

pF

Parameter Description

Test Conditions

Min

Unit

Minimum Pattern Data Retention Time

150

°

C

10

Years

125

°

C

20

Years

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM49DL640BG40IS | Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

| AM49DL640BG40IT | Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

| AM49DL640AG70IT | Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

| AM49DL640AG85IS | Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

| AM49DL640AG85IT | Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM49DL640BG30IT | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

| AM49DL640BG35IS | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

| AM49DL640BG35IT | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

| AM49DL640BG40IS | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

| AM49DL640BG40IT | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。