- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄166131 > AK4641 (Asahi Kasei Microsystems Co.,Ltd) 16 BIT CODEC WITH BLUETOOTH INTERFACE PDF資料下載

參數(shù)資料

| 型號(hào): | AK4641 |

| 廠商: | Asahi Kasei Microsystems Co.,Ltd |

| 元件分類: | Codec |

| 英文描述: | 16 BIT CODEC WITH BLUETOOTH INTERFACE |

| 中文描述: | 16位編解碼器與藍(lán)牙接口 |

| 文件頁數(shù): | 3/51頁 |

| 文件大?。?/td> | 461K |

| 代理商: | AK4641 |

第1頁第2頁當(dāng)前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁

ASAHI KASEI

[AK4641]

MS0301-E-00

2004/05

- 11 -

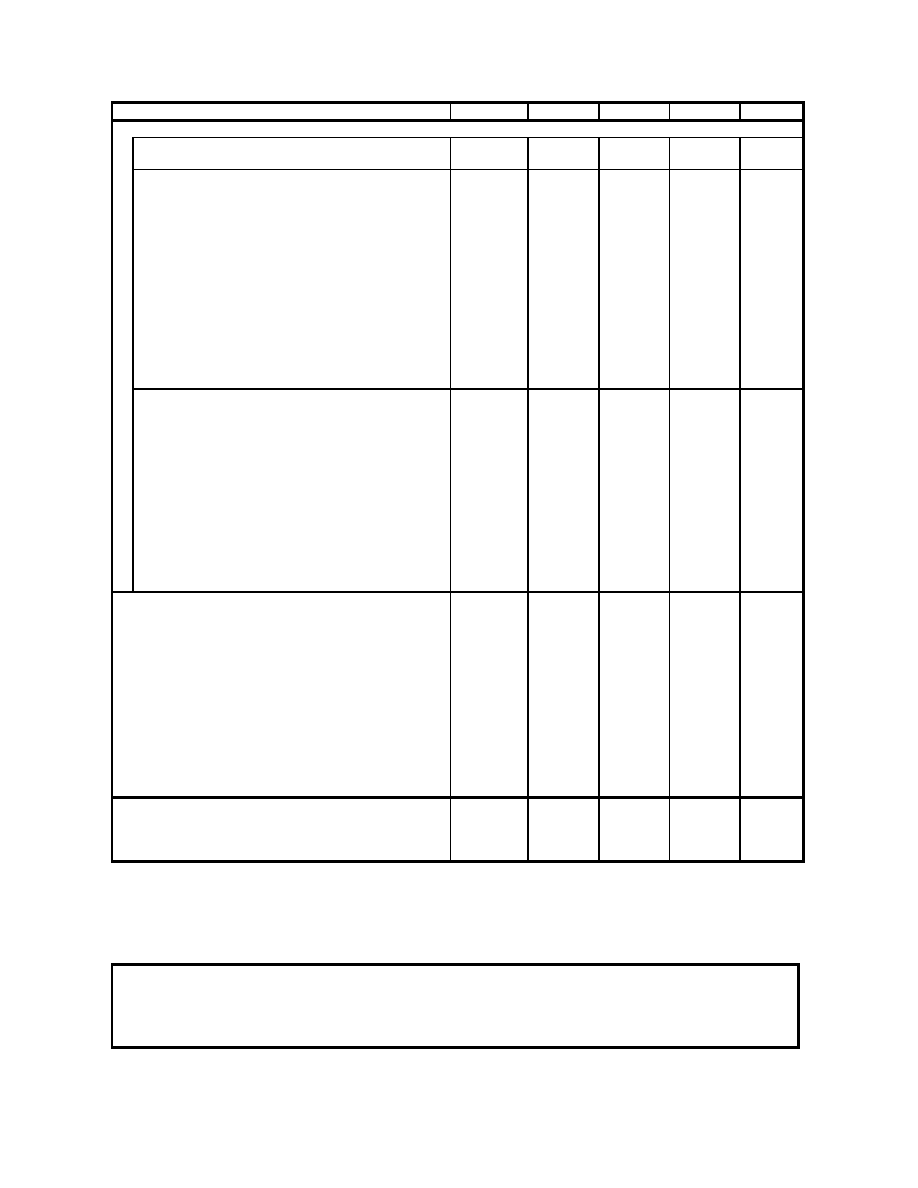

Parameter

Symbol

min

typ

max

Units

16bit Mono CODEC Interface Timing:

SYNC Timing

Frequency (PLL Lock Range)

Bfs

8

-

16

kHz

Serial Interface Timing at Short/long Frame Sync

BBICK Frequency

fBBCK

128

2048

kHz

BBICK Period

tBBCK

488

ns

BBICK duty cycle

tBDUT

50

%

BBICK Pulse Width Low

tBBCKL

200

ns

Pulse Width High

tBBCKH

200

ns

BSYNC Edge to BBICK “

↓ ”

tBSYB

50

ns

BBICK “

↓ ” to BSYNC Edge

tBBSY

50

ns

BSYNC to BSDTO (MSB) (Except Short Frame)

tBSYD

80

ns

BBICK “

↑ ” to BSDTO

tBBSD

80

ns

BSDTI Hold Time

tBSDH

50

ns

BSDTI Setup Time

tBSDS

50

ns

BSYNC Pulse Width Low

tBBSL

3300

ns

Pulse Width High

tBBSH

440

ns

Serial Interface Timing at MSB justified and I

2S

BBICK Frequency

fBBCK

256

2048

kHz

BBICK Period

tBBCK

488

ns

BBICK duty cycle

tBDUT

50

%

BBICK Pulse Width Low

tBBCKL

200

ns

Pulse Width High

tBBCKH

200

ns

BSYNC Edge to BBICK “

↑ ”

tBSYB2

50

ns

BBICK “

↑ ” to BSYNC Edge

tBBSY2

50

ns

BSYNC to BSDTO (MSB) (Except I

2S mode)

tBSYD2

80

ns

BBICK “

↓ ” to BSDTO

tBBSD2

80

ns

BSDTI Hold Time

tBSDH2

50

ns

BSDTI Setup Time

tBSDH2

50

ns

BSYNC Duty Cycle

BDuty2

45

50

55

%

Control Interface Timing (I

2C Bus mode):

SCL Clock Frequency

fSCL

-

400

kHz

Bus Free Time Between Transmissions

tBUF

1.3

-

s

Start Condition Hold Time (prior to first clock pulse)

tHD:STA

0.6

-

s

Clock Low Time

tLOW

1.3

-

s

Clock High Time

tHIGH

0.6

-

s

Setup Time for Repeated Start Condition

tSU:STA

0.6

-

s

SDA Hold Time from SCL Falling (Note 21)

tHD:DAT

0

-

s

SDA Setup Time from SCL Rising

tSU:DAT

0.1

-

s

Rise Time of Both SDA and SCL Lines

tR

-

0.3

s

Fall Time of Both SDA and SCL Lines

tF

-

0.3

s

Setup Time for Stop Condition

TSU:STO

0.6

-

s

Pulse Width of Spike Noise Suppressed by Input Filter

tSP

0

50

ns

Reset Timing

PDN Pulse Width

(Note 22)

tPD

150

ns

PMADC “

↑” to SDTO valid

(Note 23)

tPDV

2081

1/fs

PMAD2 “

↑” to BSDTO valid

(Note 24)

tBPDV

1057

1/Bfs

Note 21. Data must be held long enough to bridge the 300ns-transition time of SCL.

Note 22. The AK4641 can be reset by the PDN pin = “L”.

Note 23. This is the count of LRCK “

↑” from the PMADC bit = “1”.

Note 24. This is the count of BSYNC “

↑” from the PMAD2 bit = “1”.

Purchase of Asahi Kasei Microsystems Co., Ltd I

2C components conveys a license under the Philips

I

2C patent to use the components in the I2C system, provided the system conform to the I2C

specifications defined by Philips.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AK4641VN | 16 BIT CODEC WITH BLUETOOTH INTERFACE |

| AK4665AEN | SPECIALTY CONSUMER CIRCUIT, QCC32 |

| AK5368192WP-80 | 8M X 36 FAST PAGE DRAM MODULE, 80 ns, SMA72 |

| AK5385A | 24BIT 192KHZ ADC |

| AK8406A | AK8406A |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AK4641EN | 制造商:AKM 制造商全稱:AKM 功能描述:16bit stereo CODEC with built-in Microphone-amplifier and 16bit Mono CODEC for Bluetooth Interface. |

| AK4641VN | 制造商:AKM 制造商全稱:AKM 功能描述:16 BIT CODEC WITH BLUETOOTH INTERFACE |

| AK4642 | 制造商:AKM 制造商全稱:AKM 功能描述:16-Bit ???£ Stereo CODEC with MIC/HP/SPK-AMP |

| AK4642EN | 制造商:AKM 制造商全稱:AKM 功能描述:Stereo CODEC with MIC/HP/SPK-AMP |

| AK4642VN | 制造商:AKM 制造商全稱:AKM 功能描述:16-Bit ???£ Stereo CODEC with MIC/HP/SPK-AMP |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。