- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16542 > ADP5585CP-EVALZ (Analog Devices Inc)BOARD EVAL FOR ADP5585CP PDF資料下載

參數(shù)資料

| 型號(hào): | ADP5585CP-EVALZ |

| 廠商: | Analog Devices Inc |

| 文件頁(yè)數(shù): | 6/40頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | BOARD EVAL FOR ADP5585CP |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 主要目的: | 接口,GPIO 擴(kuò)展器 |

| 已用 IC / 零件: | ADP5585 |

| 主要屬性: | 10 個(gè)可配置的 I/O |

| 次要屬性: | I²C 接口 |

| 已供物品: | 板 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)

ADP5585

Data Sheet

Rev. C | Page 14 of 40

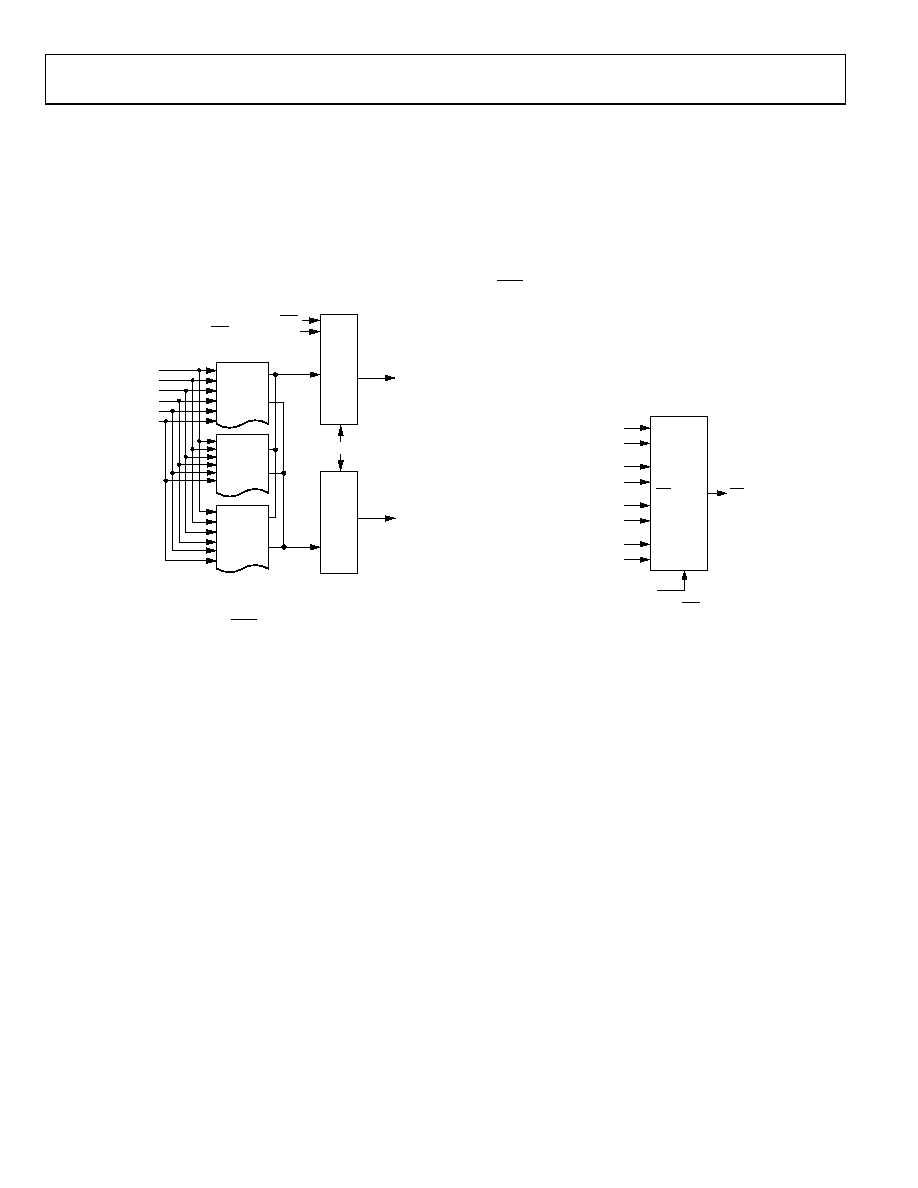

RESET BLOCKS

ADP5585 features two reset blocks that can generate reset con-

ditions if certain events are detected simultaneously. Up to three

reset trigger events can be programmed for RESET1. Up to two

reset trigger events can be programmed for RESET2. The event

scan control blocks monitor whether these events are present for

the duration of RESET_TRIG_TIME[2:0] (Register 0x2E,

Bits[4:2]). If they are, reset-initiate signals are sent to the reset

generator blocks. The generated reset signal pulse width is

programmable.

RESET_PULSE_WIDTH[1:0]

RESET_TRIG_TIME[2:0]

RESET1_EVENT_A[7:0]

RESET1_EVENT_B[7:0]

RESET1_EVENT_C[7:0]

KEY

SCAN

CONTROL

RST_PASSTHRU_EN

RST

(R4)

RESET1

GPI

SCAN

CONTROL

LOGIC

BLOCK

CONTROL

RESET2_EVENT_A[7:0]

RESET2_EVENT_B[7:0]

(C4)

RESET2

RESET1_

INITIATE

RESET2_

INITIATE

RESET

GEN 2

RESET

GEN 1

09841-

020

Figure 21. Reset Blocks

The Reset 1 signal uses the R4 I/O pin as its output. A pass

through mode allows the main RST pin to be output on the R4

pin also. The Reset 2 signal uses the C4 I/O pin as its output.

The reset generation signals are useful in situations where the

system processor has locked up and the system is unresponsive

to input events. The user can press one of the reset event combi-

nations and initiate a system wide reset. This alleviates the need

for removing the battery from the system and doing a hard reset.

It is not recommended to use the immediate trigger time (see

Table 54) because this setting may cause false triggering.

Interrupts

The INT pin can be asserted low if any of the internal interrupt

sources is active. The user can select which internal interrupts

interact with the external interrupt pin in Register 0x3C (refer

to Table 68). Register 0x3B allows the user to choose whether

the external interrupt pin remains asserted, or deasserts for

50 s, then reasserts, in the case that there are multiple internal

interrupts asserted and one is cleared (refer to Table 67).

EVENT_INT

EVENT_IEN

INT DRIVE

INT

INT_CFG

GPI_INT

GPI_IEN

LOGIC_INT

LOGIC_IEN

OVRFLOW_INT

OVRFLOW_IEN

09841-

021

Figure 22. Asserting INT Low

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EBM25DSEF-S13 | CONN EDGECARD 50POS .156 EXTEND |

| GSC06DRTH-S734 | CONN EDGECARD 12POS DIP .100 SLD |

| 5503995-4 | CABLE ASSEM FIBER ST-ST 5 METER |

| ADA4853-3YRU-EBZ | BOARD EVAL FOR ADA4853-3YRU |

| A3CCB-2636G | IDC CABLE- AKC26B/AE26G/AKC26B |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADP5586 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Keypad Decoder and I/O Port Expander |

| ADP5586ACBZ-00-R7 | 功能描述:接口-I/O擴(kuò)展器 RoHS:否 制造商:NXP Semiconductors 邏輯系列: 輸入/輸出端數(shù)量: 最大工作頻率:100 kHz 工作電源電壓:1.65 V to 5.5 V 工作溫度范圍:- 40 C to + 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:HVQFN-16 封裝:Reel |

| ADP5586ACBZ-01-R7 | 功能描述:接口-I/O擴(kuò)展器 RoHS:否 制造商:NXP Semiconductors 邏輯系列: 輸入/輸出端數(shù)量: 最大工作頻率:100 kHz 工作電源電壓:1.65 V to 5.5 V 工作溫度范圍:- 40 C to + 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:HVQFN-16 封裝:Reel |

| ADP5586ACBZ-03-R7 | 功能描述:接口-I/O擴(kuò)展器 RoHS:否 制造商:NXP Semiconductors 邏輯系列: 輸入/輸出端數(shù)量: 最大工作頻率:100 kHz 工作電源電壓:1.65 V to 5.5 V 工作溫度范圍:- 40 C to + 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:HVQFN-16 封裝:Reel |

| ADP5586CB-EVALZ | 功能描述:界面開發(fā)工具 RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評(píng)估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。