- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374022 > ADP3510 (Analog Devices, Inc.) Secondary Over-Voltage Protection for 2-4 cell in series Li-Ion/Poly (4.40V) 8-SM8 -40 to 110 PDF資料下載

參數(shù)資料

| 型號: | ADP3510 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Secondary Over-Voltage Protection for 2-4 cell in series Li-Ion/Poly (4.40V) 8-SM8 -40 to 110 |

| 中文描述: | CDMA的電源管理系統(tǒng) |

| 文件頁數(shù): | 3/16頁 |

| 文件大?。?/td> | 283K |

| 代理商: | ADP3510 |

REV. 0

–3–

ADP3510

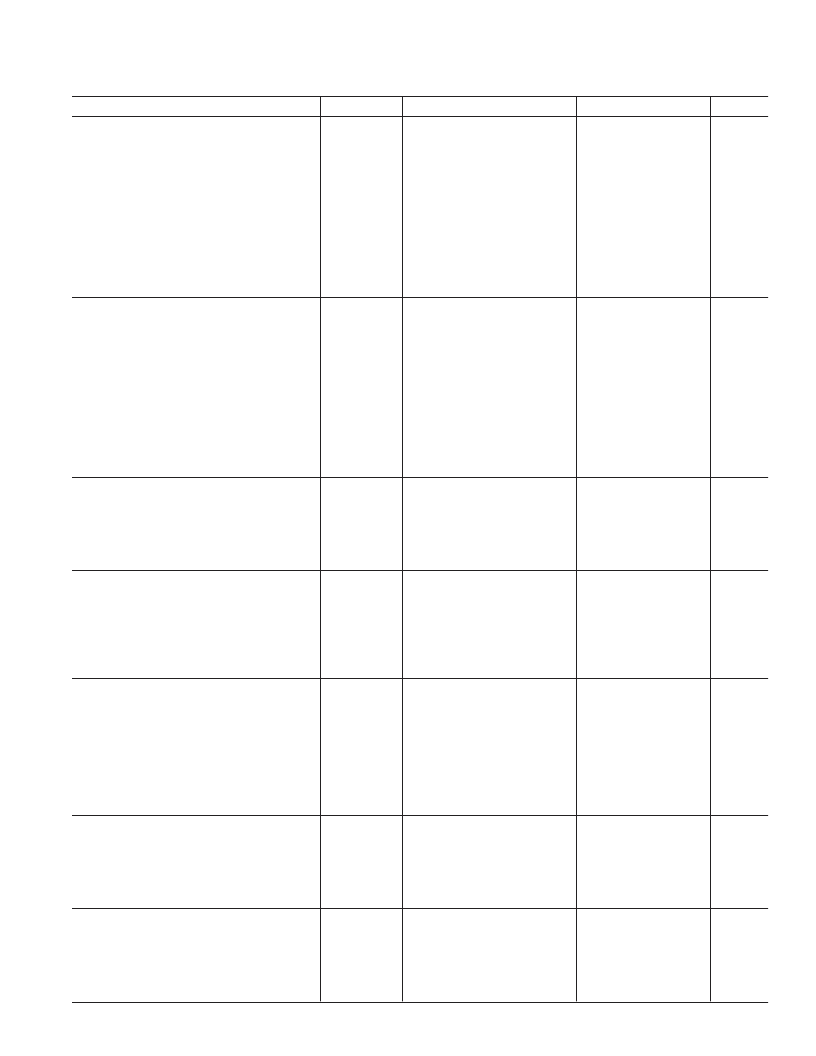

Parameter

ANALOG LDO (VAN)

Output Voltage

Line Regulation

Load Regulation

Output Capacitor Required for Stability

Dropout Voltage

Symbol

Conditions

Min

Typ

Max

Unit

VAN

D

VAN

D

VAN

C

O

V

DO

Line, Load, Temp

Minimum Load

50

m

A

£

I

LOAD

£

75 mA

2.85

2.935

3.02

1

6

V

mV

mV

m

F

2.2

V

O

= V

INITIAL

100 mV

I

LOAD

= 75 mA

f = 217 Hz (T = 4.6 ms)

VBAT = 3.6 V

f = 10 Hz to 100 kHz

I

LOAD

= 75 mA

VBAT = 3.6 V

100

75

175

mV

dB

Ripple Rejection

D

VBAT/

D

VAN

V

NOISE

Output Noise Voltage

80

m

V rms

TCXO LDO (VTCXO)

Output Voltage

Line Regulation

Load Regulation

Output Capacitor Required for Stability

Dropout Voltage

VTCXO

D

VTCXO

D

VTCXO

C

O

V

DO

Line, Load, Temp

Minimum Load

50

m

A

£

I

LOAD

£

10 mA

2.71

2.765 2.82

1

3

V

mV

mV

m

F

mV

0.47

V

O

= V

INITIAL

– 100 mV

I

LOAD

= 10 mA

f = 217 Hz (T = 4.6 ms)

VBAT = 3.6 V

f = 10 Hz to 100 kHz

I

LOAD

= 10 mA

VBAT = 3.6 V

175

Ripple Rejection

D

VBAT/

D

VTCXO

V

NOISE

75

dB

Output Noise Voltage

80

m

V rms

REAL-TIME CLOCK LDO/

BATTERY CHARGER (VRTC)

Maximum Output Voltage

Off Reverse Input Current

Dropout Voltage

VRTC

I

L

V

DO

1

m

A

£

I

LOAD

£

6

m

A

2.0 V < VBAT < UVLO

V

O

= V

INITIAL

– 100 mV

I

LOAD

= 10

m

A

2.77

2.85

2.93

1

175

V

m

A

mV

MEMORY LDO (VMEM)

Output Voltage

Line Regulation

Load Regulation

Output Capacitor Required for Stability

Dropout Voltage

VMEM

D

VMEM

D

VMEM

C

O

V

DO

Line, Load, Temp

Minimum Load

50

m

A

£

I

LOAD

£

60 mA

2.85

2.935 3.02

1

5

2.2

100

V

mV

mV

m

F

mV

V

O

= V

INITIAL

– 100 mV

I

LOAD

= 60 mA

175

REFOUT

Output Voltage

Line Regulation

Load Regulation

VREFOUT

D

VREFOUT Minimum Load

D

VREFOUT 0

m

A

£

I

LOAD

50

m

A

VBAT = 3.6 V

D

VBAT/

f = 217 Hz (T = 4.6 ms)

D

VREFOUT VBAT = 3.6 V

C

O

V

NOISE

f = 10 Hz to 100 kHz

Line, Load, Temp

1.19

1.210 1.23

0.3

0.6

V

mV

mV

Ripple Rejection

75

dB

Maximum Capacitive Load

Output Noise Voltage

RESET GENERATOR (RESET)

Output High Voltage

Output Low Voltage

Output Current

Delay Time per Unit Capacitance

Applied to RESCAP Pin

SEQUENCING

Delay Time per Unit Capacitance

Applied to PDCAP Pin

PDCAP Charging Current

VAN Discharge Resistance

VIO Discharge Resistance

100

40

pF

mV rms

V

OH

V

OL

I

OL

/I

OH

T

D

I

OH

= +500

m

A

I

OL

= –500

m

A

2.4

V

V

mA

ms/nF

0.25

1

4.0

0.8

1.5

T

D

0.3

0.8

3.0

ms/nF

I

OH

V

PDCAP

= 0

2.5

5

200

200

8

m

A

W

W

相關PDF資料 |

PDF描述 |

|---|---|

| ADP3510ARU | Secondary Over-Voltage Protection for 2-4 cell in series Li-Ion/Poly (4.40V) 8-SM8 -40 to 110 |

| ADP3522 | GSM Power Management System |

| ADP3522ACP-1.8 | GSM Power Management System |

| ADP3522ACP-3 | GSM Power Management System |

| ADP3604 | |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ADP3510ARU | 制造商:AD 制造商全稱:Analog Devices 功能描述:CDMA Power Management System |

| ADP3510ARU-REEL7 | 制造商:Analog Devices 功能描述: |

| ADP3522 | 制造商:AD 制造商全稱:Analog Devices 功能描述:GSM Power Management System |

| ADP3522ACP-1.8 | 制造商:AD 制造商全稱:Analog Devices 功能描述:GSM Power Management System |

| ADP3522ACP-1.8-RL | 制造商:Analog Devices 功能描述:GSM Power Management System 32-Pin LFCSP EP T/R |

發(fā)布緊急采購,3分鐘左右您將得到回復。