- 您現在的位置:買賣IC網 > PDF目錄17059 > AD9114-DPG2-EBZ (Analog Devices Inc)IC DAC DUAL 8BIT LO PWR 40LFCSP PDF資料下載

參數資料

| 型號: | AD9114-DPG2-EBZ |

| 廠商: | Analog Devices Inc |

| 文件頁數: | 43/52頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC DAC DUAL 8BIT LO PWR 40LFCSP |

| 標準包裝: | 1 |

| 系列: | TxDAC® |

| DAC 的數量: | 2 |

| 位數: | 8 |

| 采樣率(每秒): | 125M |

| 數據接口: | 串行 |

| DAC 型: | 電流 |

| 工作溫度: | -40°C ~ 85°C |

| 已供物品: | 板 |

| 已用 IC / 零件: | AD9114 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁當前第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

AD9114/AD9115/AD9116/AD9117

Data Sheet

Rev. C | Page 48 of 52

DIFFERENTIAL BUFFERED OUTPUT

USING AN OP AMP

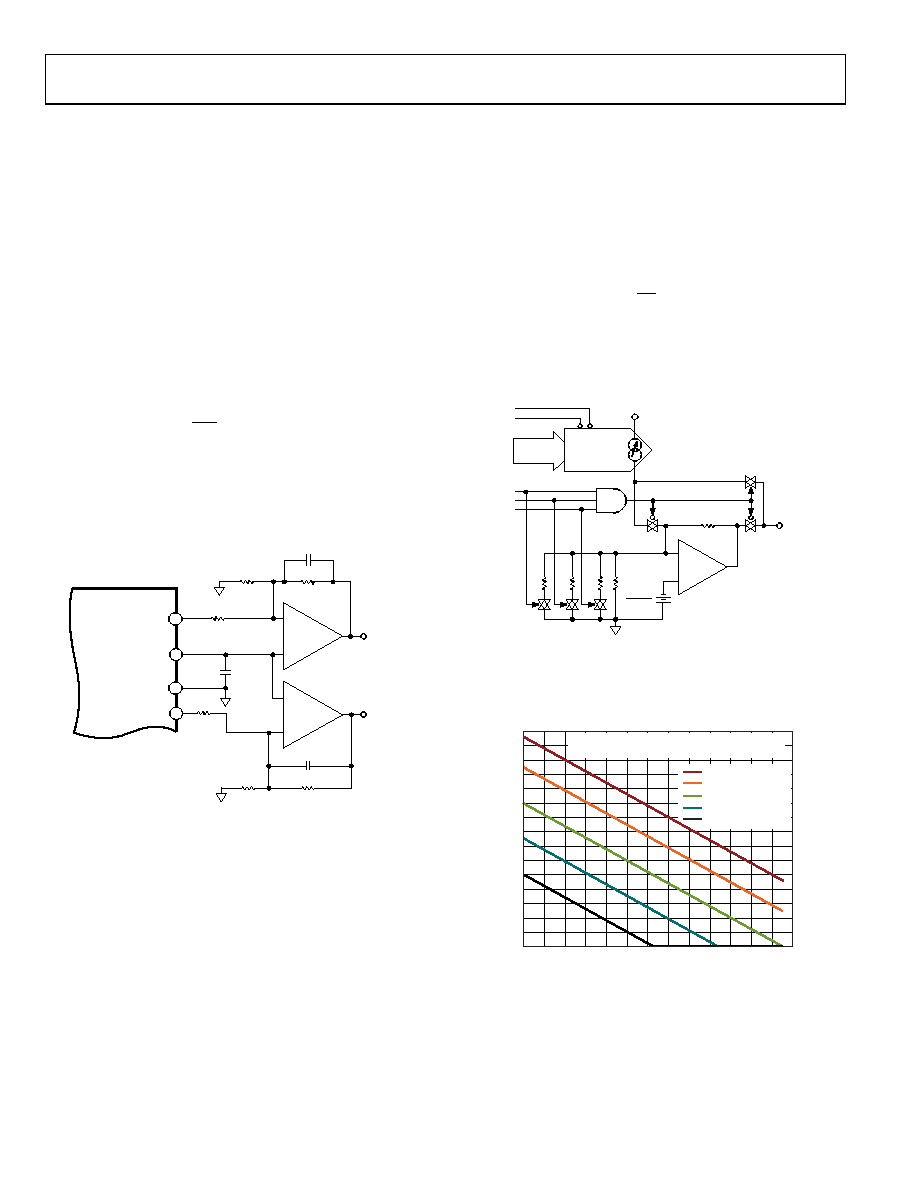

A dual op amp (see the circuit shown in Figure 104) can be

used in a differential version of the single-ended buffer shown

in Figure 103. Figure 104 is a simplified schematic. The REFIO

pin must be buffered to keep the load current less than 100 nA.

The same RC network is used to form a one-pole differential,

low-pass filter to isolate the op amp inputs from the high

frequency images produced by the DAC outputs. The feedback

resistors, RFB, determine the differential peak-to-peak signal swing

by the formula

VOUT = 2 × RFB × IFS

The maximum and minimum single-ended voltages out of the

amplifier are, respectively,

+

×

=

B

FB

REF

MAX

R

V

1

VMIN = VMAX RFB × IFS

The common-mode voltage of the differential output is

determined by the formula

VCM = VMAX RFB × IFS

AD9114/AD9115/

AD9116/AD9117

IOUTP

IOUTN

RFB

VOUT

REFIO 34

28

RS

AVSS 25

CF

C

RFB

RB

CF

RS

RB

29

+

–

ADA4841-2

+

–

ADA4841-2

07466-

065

Figure 104. Single-Supply Differential Buffer

AUXILIARY DACs

The DACs of the AD9114/AD9115/AD9116/AD9117 feature

two versatile and independent 10-bit auxiliary DACs suitable

for dc offset correction and similar tasks.

Because the AUXDACs are driven through the SPI port, they

should never be used in timing-critical applications, such as

inside analog feedback loops.

To keep the pin count reasonable, these auxiliary DACs each

share a pin with the corresponding FSADJx resistor. They are,

therefore, usable only when enabled and when that DAC is

operated on its internal full-scale resistors. A simple I-to-V

converter is implemented on-chip with selectable shunt resistors

(3.2 kΩ to 16 kΩ) such that if REFIO is set to exactly 1 V, REFIO/2

equals 0.5 V and the following equation describes the no load

output voltage:

kΩ

16

5

.

1

V

5

.

0

=

S

DAC

OUT

R

I

V

Figure 105 illustrates the function of all the SPI bits controlling

these DACs with the exception of the QAUXEN (Register 0x0A)

and IAUXEN (Register 0x0C) bits and gating to prohibit

RS < 3.2 kΩ.

+

–

OP AMP

AUXDAC

[9:0]

AVDD

RNG0

RNG1

REFIO

2

16k 16k

16k

4k 8k

OFS2

OFS1

OFS0

(OFS > 4 = 4)

AUX

PIN

RNG: 00 = 125A

fS

01 = 62A

fS

10 = 31A

fS

11 = 16A

fS

07466-

066

Figure 105. AUXDAC Simplified Circuit Diagram

The SPI speed limits the update rate of the auxiliary DACs. The

data is inverted such that IAUXDAC is full scale at 0x000 and zero

at 0x1FF, as shown in Figure 106.

3.0

2.8

2.6

2.4

2.2

2.0

1.8

1.6

1.4

1.2

1.0

0.8

0.6

0.4

0.2

0

10

20

30

40

50

60

70

80

90

100

120 130

DAC CURRENT (A)

O

U

T

PU

T

(V)

110

ROFFSET = 3.3k

ROFFSET = 4k

ROFFSET = 5.3k

ROFFSET = 8k

ROFFSET = 16k

OP AMP OUTPUT VOLTAGE vs.

CHANGES IN ROFFSET AND DAC CURRENT IN A

07466-

067

Figure 106. AUXDAC Op Amp Output vs. Current, AVDD = 3.3 V No Load,

AUXDAC 0x1FF to 0x000

相關PDF資料 |

PDF描述 |

|---|---|

| AD9115-DPG2-EBZ | IC DAC DUAL 10BIT LO PWR 40LFCSP |

| 0210490184 | CABLE JUMPER 1.25MM .229M 12POS |

| RCM15DCCN-S189 | CONN EDGECARD 30POS R/A .156 SLD |

| CDB4382A | BOARD EVAL FOR CS4382A DAC |

| 0210490183 | CABLE JUMPER 1.25MM .229M 12POS |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9114-EBZ | 制造商:Analog Devices 功能描述:DUAL 8 BIT LOW POWER CONVERTER - Boxed Product (Development Kits) |

| AD9115 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Dual, 8-/10-/12-/14-Bit Low Power Digital-to-Analog Converters |

| AD91151Z | 制造商:Analog Devices 功能描述: |

| AD91154Z | 制造商:Analog Devices 功能描述:SCREENED DSP PART - Rail/Tube |

| AD91156-05 | 制造商:Analog Devices 功能描述:IC,ADSP-BF561SKB600,16BIT,600MHZ,DUAL CO |

發(fā)布緊急采購,3分鐘左右您將得到回復。