- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1890 > AD5522JSVUZ (Analog Devices Inc)IC PMU QUAD 16BIT DAC 80-TQFP PDF資料下載

參數(shù)資料

| 型號(hào): | AD5522JSVUZ |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 3/64頁 |

| 文件大小: | 0K |

| 描述: | IC PMU QUAD 16BIT DAC 80-TQFP |

| 產(chǎn)品變化通告: | Improve FI ac crosstalk |

| 設(shè)計(jì)資源: | Parametric Measurement Unit and Supporting Components for PAD Appls Using AD5522 and AD7685 (CN0104) |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 類型: | 每引腳參數(shù)測(cè)量單元(PPMU) |

| 應(yīng)用: | 自動(dòng)測(cè)試設(shè)備 |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 80-TQFP 裸露焊盤 |

| 供應(yīng)商設(shè)備封裝: | 80-TQFP-EP(12x12) |

| 包裝: | 托盤 |

第1頁第2頁當(dāng)前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

Data Sheet

AD5522

Rev. E | Page 11 of 64

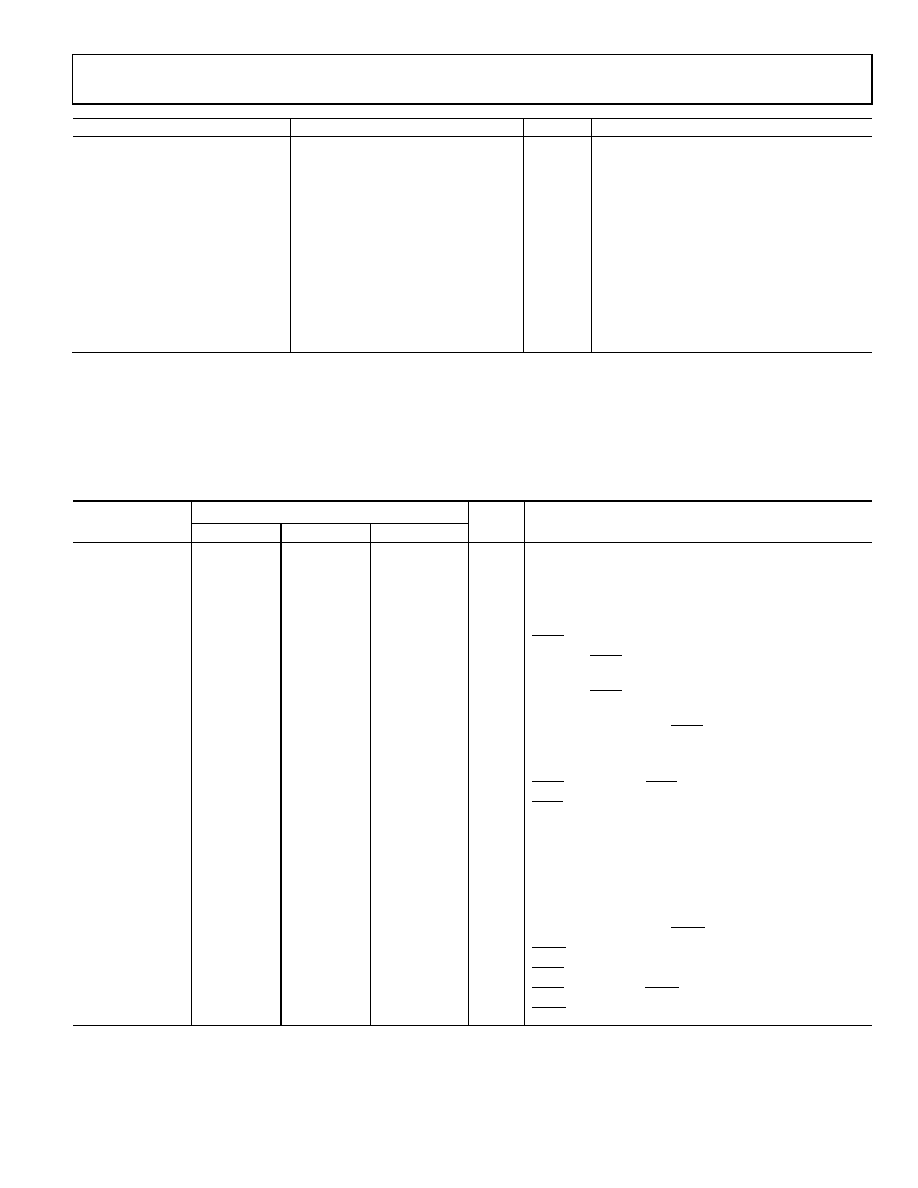

Parameter

Min

Typ 1

Max

Unit

Test Conditions/Comments

Power Supply Sensitivity2

From dc to 1 kHz

ΔForced Voltage/ΔAVDD

80

dB

ΔForced Voltage/ΔAVSS

80

dB

ΔMeasured Current/ΔAVDD

85

dB

ΔMeasured Current/ΔAVSS

75

dB

ΔForced Current/ΔAVDD

75

dB

ΔForced Current/ΔAVSS

75

dB

ΔMeasured Voltage/ΔAVDD

85

dB

ΔMeasured Voltage/ΔAVSS

80

dB

ΔForced Voltage/ΔDVCC

90

dB

ΔMeasured Current/ΔDVCC

90

dB

ΔForced Current/ΔDVCC

90

dB

ΔMeasured Voltage/ΔDVCC

90

dB

1

Typical specifications are at 25°C and nominal supply, ±15.25 V, unless otherwise noted.

2

Guaranteed by design and characterization; not production tested. Tempco values are mean and standard deviation, unless otherwise noted.

TIMING CHARACTERISTICS

AVDD ≥ 10 V, AVSS ≤ 5 V, |AVDD AVSS| ≥ 20 V and ≤ 33 V, DVCC = 2.3 V to 5.25 V, VREF = 5 V, TJ = 25°C to 90°C, unless

otherwise noted.

Table 2. SPI Interface

DVCC, Limit at TMIN, TMAX

Unit

Description

2.3V to 2.7V

2.7V to 3.6V

4.5V to 5.25V

tWRITE4

1030

735

ns min

Single channel update cycle time (X1 register write)

950

655

ns min

Single channel update cycle time (any other register write)

t1

30

20

ns min

SCLK cycle time

t2

8

ns min

SCLK high time

t3

8

ns min

SCLK low time

t4

10

ns min

SYNC falling edge to SCLK falling edge setup time

150

ns min

Minimum SYNC high time in write mode after X1 register

write (one channel)

70

ns min

Minimum SYNC high time in write mode after any

other register write

t6

10

5

ns min

29th SCLK falling edge to SYNC rising edge

t7

5

ns min

Data setup time

t8

9

7

4.5

ns min

Data hold time

t9

120

75

55

ns max

SYNC rising edge to BUSY falling edge

t10

BUSY pulse width low for X1 and some PMU register writes;

1 DAC X1

1.65

s max

2 DAC X1

2.3

s max

3 DAC X1

2.95

s max

4 DAC X1

3.6

s max

Other Registers

270

ns max

System control register/PMU registers

t11

20

ns min

29th SCLK falling edge to LOAD falling edge

t12

20

ns min

LOAD pulse width low

t13

150

ns min

BUSY rising edge to FOHx output response time

t14

0

ns min

BUSY rising edge to LOAD falling edge

t15

100

ns max

LOAD falling edge to FOHx output response time

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD5532ABC-5 | IC DAC 14BIT 32CH 74-CSPBGA |

| AD5532HSABC | IC DAC 14BIT 32CH 74-CSPBGA |

| AD5535ABCZ | IC DAC 14BIT 32CHAN 124CSPBGA |

| AD5547BRU | IC DAC 16BIT DUAL 38-TSSOP |

| AD5560JSVUZ-REEL | IC DPS PROGRAMABLE W/DAC 64TQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD5522JSVUZ-RL | 功能描述:Per-Pin Parametric Measurement Unit (PPMU) IC Automatic Test Equipment 80-TQFP-EP (12x12) 制造商:analog devices inc. 系列:- 包裝:帶卷(TR) 零件狀態(tài):有效 類型:每引腳參數(shù)測(cè)量單元(PPMU) 應(yīng)用:自動(dòng)測(cè)試設(shè)備 安裝類型:表面貼裝 封裝/外殼:80-TQFP 裸露焊盤 供應(yīng)商器件封裝:80-TQFP-EP(12x12) 標(biāo)準(zhǔn)包裝:1,000 |

| AD5523JCPZ | 制造商:AD 制造商全稱:Analog Devices 功能描述:Quad Parametric Measurement Unit With Integrated 16-Bit Level Setting DACs |

| AD5530 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Serial Input, Voltage Output 12-/14-Bit DACs |

| AD5530_07 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Serial Input, Voltage Output 12-/14-Bit Digital-to-Analog Converters |

| AD5530BRU | 制造商:Analog Devices 功能描述:DAC 1-CH R-2R 12-bit 16-Pin TSSOP 制造商:Rochester Electronics LLC 功能描述:12-BIT VOLTAGE OUTPUT DAC I.C. - Bulk 制造商:Analog Devices 功能描述:IC 12BIT DAC SMD 5530 TSSOP16 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。