- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄298813 > ACT-7000ASC-300F17I 64-BIT, 300 MHz, RISC PROCESSOR, CQFP208 PDF資料下載

參數(shù)資料

| 型號(hào): | ACT-7000ASC-300F17I |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 64-BIT, 300 MHz, RISC PROCESSOR, CQFP208 |

| 封裝: | 1.120 X 1.120 INCH, CERAMIC, QFP-208 |

| 文件頁(yè)數(shù): | 4/26頁(yè) |

| 文件大小: | 231K |

| 代理商: | ACT-7000ASC-300F17I |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)

12

SCD7000A Rev C 9/9/09

Aeroflex Plainview

factor between SysClock and the pipeline clock, the

ACT 7000ASC also allows half-integral multipliers,

thereby providing greater granularity in the designers

choice of pipeline and system interface frequencies.

The interface consists of a 64-bit Address/Data bus with

8 check bits and a 9-bit command bus. In addition, there are

six handshake signals and six interrupt inputs. The

interface has a simple timing specification and is capable of

transferring data between the processor and memory at a

peak rate of 600 MB/sec with a 75 MHz SysClock.

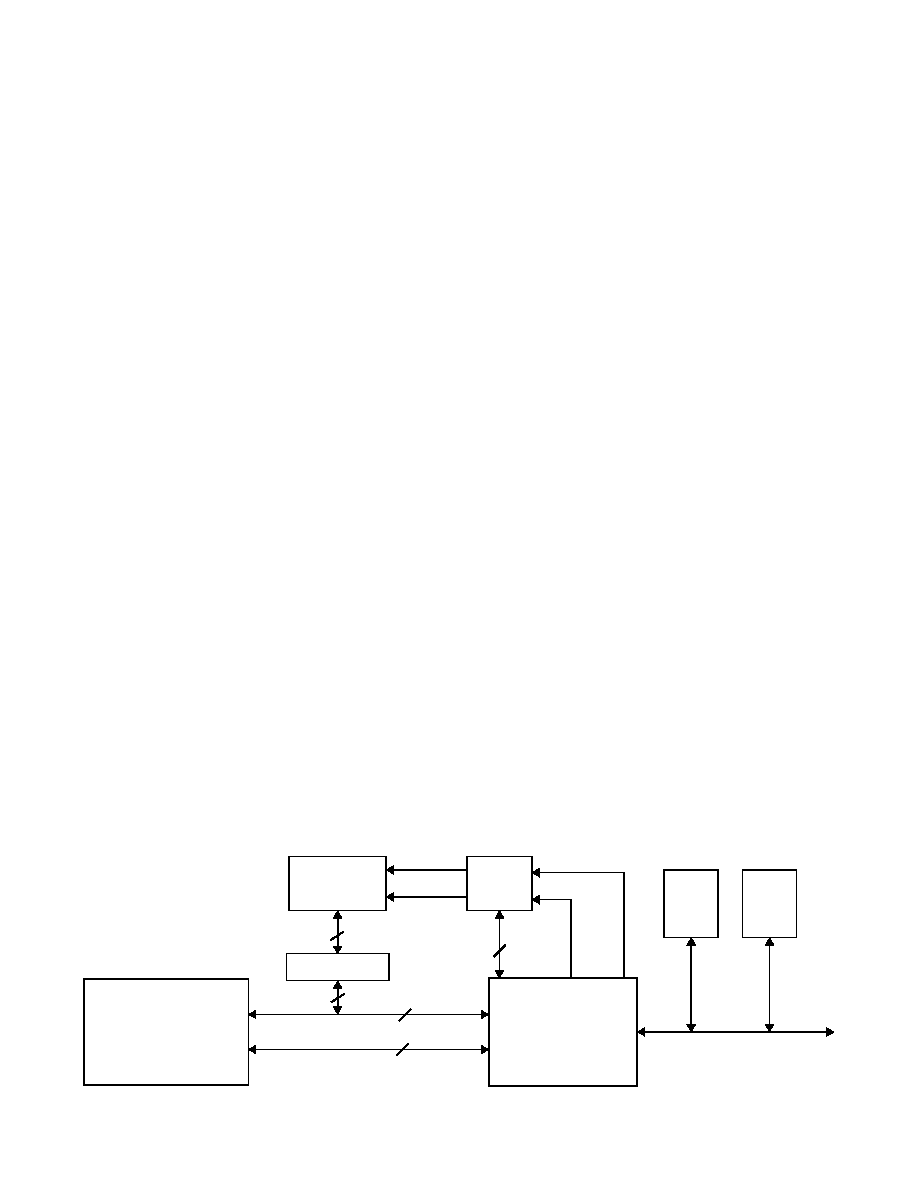

Figure 6 shows a typical embedded system using the

ACT 7000ASC. This example shows a system with a bank

of DRAMs, and an interface ASIC which provides DRAM

control as well as an I/O port.

System Address/Data Bus

The 64-bit System Address Data (SysAD) bus is used to

transfer addresses and data between the ACT 7000ASC

and the rest of the system. It is protected with an 8-bit parity

check bus, SysADC.

The system interface is configurable to allow easy

interfacing to memory and I/O systems of varying

frequencies. The data rate and the bus frequency at which

the ACT 7000ASC transmits data to the system interface

are programmable via boot time mode control bits. Also,

the rate at which the processor receives data is fully

controlled by the external device. Therefore, either a low

cost interface requiring no read or write buffering or a

faster, high-performance interface can be designed to

communicate with the ACT 7000ASC. Again, the system

designer

has

the

flexibility

to

make

these

price/performance trade-offs.

System Command Bus

The ACT 7000ASC interface has a 9-bit System

Command (SysCmd) bus. The command bus indicates

whether the SysAD bus carries an address or data. If the

SysAD bus carries an address, then the SysCmd bus also

indicates what type of transaction is to take place (for

example, a read or write). If the SysAD bus carries data,

then the SysCmd bus also gives information about the data

(for example, this is the last data word transmitted, or the

data contains an error). The SysCmd bus is bidirectional to

support both processor requests and external requests to the

ACT 7000ASC. Processor requests are initiated by the

ACT 7000ASC and responded to by an external device.

External requests are issued by an external device and

require the ACT 7000ASC to respond.

The ACT 7000ASC supports one to eight byte and

32-byte block transfers on the SysAD bus. In the case of a

sub-double-word transfer, the 3 low-order address bits give

the byte address of the transfer, and the SysCmd bus

indicates the number of bytes being transferred.

Handshake Signals

There are six handshake signals on the system interface.

Two of these, RdRdy* and WrRdy*, are used by an

external device to indicate to the ACT 7000ASC whether it

can accept a new read or write transaction. The

ACT 7000ASC samples these signals before deasserting

the address on read and write requests.

ExtRqst* and Release* are used to transfer control of

the SysAD and SysCmd buses from the processor to an

external device. When an external device needs to control

the interface, it asserts ExtRqst*. The ACT 7000ASC

responds by asserting Release* to release the system

interface to slave state.

ValidOut*

and

ValidIn*

are

used

by

the

ACT 7000ASC and the external device respectively to

indicate that there is a valid command or data on the SysAD

and SysCmd buses. The ACT 7000ASC asserts ValidOut*

when it is driving these buses with a valid command or

data, and the external device drives ValidIn* when it has

control of the buses and is driving a valid command or data.

System Interface Operation

The ACT 7000ASC can issue read and write requests to

an external device, while an external device can issue null

and write requests to the ACT 7000ASC.

For

processor

reads,

the

ACT 7000ASC

asserts

ValidOut* and simultaneously drives the address and read

command on the SysAD and SysCmd buses. If the system

interface has RdRdy* asserted, then the processor tristates

its drivers and releases the system interface to slave state by

asserting Release*. The external device can then begin

sending data to the ACT 7000ASC.

PCI Bus

XX

Control

DRAM

Latch

72

25

SysAD Bus

SysCmd

Memory I/O

Controller

Flash /

Address

Boot

ROM

ACT 7000ASC

8

Figure 6 – Typical Embedded System Block Diagram

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ACT4445 | DATACOM, MIL-STD-1553 DATA BUS TRANSCEIVER, BCC64 |

| ACTS04KMSR-02 | ACT SERIES, HEX 1-INPUT INVERT GATE, CDFP14 |

| ACTS04DMSR-02 | ACT SERIES, HEX 1-INPUT INVERT GATE, CDIP14 |

| ACTS08DMSR | ACT SERIES, QUAD 2-INPUT AND GATE, CDIP14 |

| ACTS138HMSR-02 | ACT SERIES, OTHER DECODER/DRIVER, INVERTED OUTPUT, UUC16 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ACT7000SC | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:ACT 7000SC 64-Bit Superscaler Microprocessor |

| ACT-7000SC-150F17C | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:ACT 7000SC 64-Bit Superscaler Microprocessor |

| ACT-7000SC-150F17I | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:ACT 7000SC 64-Bit Superscaler Microprocessor |

| ACT-7000SC-150F17M | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:ACT 7000SC 64-Bit Superscaler Microprocessor |

| ACT-7000SC-150F17Q | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:ACT 7000SC 64-Bit Superscaler Microprocessor |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。