- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄298813 > ACT-7000ASC-300F17I 64-BIT, 300 MHz, RISC PROCESSOR, CQFP208 PDF資料下載

參數(shù)資料

| 型號: | ACT-7000ASC-300F17I |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 64-BIT, 300 MHz, RISC PROCESSOR, CQFP208 |

| 封裝: | 1.120 X 1.120 INCH, CERAMIC, QFP-208 |

| 文件頁數(shù): | 22/26頁 |

| 文件大小: | 231K |

| 代理商: | ACT-7000ASC-300F17I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當(dāng)前第22頁第23頁第24頁第25頁第26頁

5

SCD7000A Rev C 9/9/09

Aeroflex Plainview

view of the processors operation however since the

out-of-order completion of loads, stores, and long latency

floating-point operations can result in there being even

more instructions in process than what is shown.

Note that instruction dependencies, resource conflicts,

and branches result in some of the instruction slots being

occupied by NOPs.

Integer Unit

Like the ACT 52xx family, the

ACT 7000ASC

implements the MIPS IV Instruction Set Architecture, and

is therefore fully upward compatible with applications that

run on processors such as the R4650 and R4700 that

implement the earlier generation MIPS III Instruction Set

Architecture. Additionally, the ACT 7000ASC includes

two implementation specific instructions not found in the

baseline MIPS IV ISA, but that are useful in the embedded

market place. Described in detail in a later section of this

datasheet,

these

instructions

are

integer

multiply-accumulate and three-operand integer multiply.

The

ACT 7000ASC integer unit includes thirty-two

general purpose 64-bit registers, the HI/LO result registers

for the two-Pipeline operand integer multiply/divide

operations, and the program counter, or PC. There are two

separate execution units, one of which can execute

function, or F, type instructions and one which can execute

memory, or M, type instructions. See above for a

description of the instruction types and the issue rules. As

a special case, integer multiply/divide instructions as well

as their corresponding MFHi and MFLo instructions can

only be executed in the F type execution unit. Within each

execution unit the operational characteristics are the same

as on previous MIPS designs with single cycle ALU

operations (add, sub, logical, shift), one cycle load delay,

and an autonomous multiply/divide unit.

Register File

The

ACT 7000ASC has thirty-two general purpose

registers with register location (r0) hard wired to zero

value. These registers are used for scalar integer operations

and address calculation. In order to service the two integer

execution units, the register file has four read ports and two

write ports and is fully bypassed both within and between

the two execution units to minimize operation latency in

the pipeline.

ALU

The ACT 7000ASC has two complete integer ALU’s

each consisting of an integer adder/subtractor, a logic unit,

and a shifter. Table 3 shows the functions performed by the

ALU’s for each execution unit. Each of these units is

optimized to perform all operations in a single processor

cycle.

Integer Multiply/Divide

The ACT 7000ASC has a single dedicated integer

multiply/divide unit optimized for high-speed multiply and

multiply-accumulate operations. The multiply/divide unit

resides in the F type execution unit. Table 4 shows the

performance of the multiply/divide unit on each operation.

The baseline MIPS IV ISA specifies that the results of a

multiply or divide operation be placed in the Hi and Lo

registers. These values can then be transferred to the

general purpose register file using the Move-from-Hi and

Move-from-Lo (MFHI/MFLO) instructions.

In addition to the baseline MIPS IV integer multiply

instructions, the ACT 7000ASC also implements the

3-operand multiply instruction, MUL. This instruction

specifies that the multiply result go directly to the integer

register file rather than the Lo register. The portion of the

multiply that would have normally gone into the Hi register

is discarded. For applications where it is known that the

upper half of the multiply result is not required, using the

MUL instruction eliminates the necessity of executing an

explicit MFLO instruction.

Also

included

in

the

ACT 7000ASC

are

the

multiply-add instructions MAD/MADU. This instruction

multiplies two operands and adds the resulting product to

the current contents of the Hi and Lo registers. The

multiply-accumulate operation is the core primitive of

almost all signal processing algorithms allowing the

ACT 7000ASC to eliminate the need for a separate DSP

engine in many embedded applications.

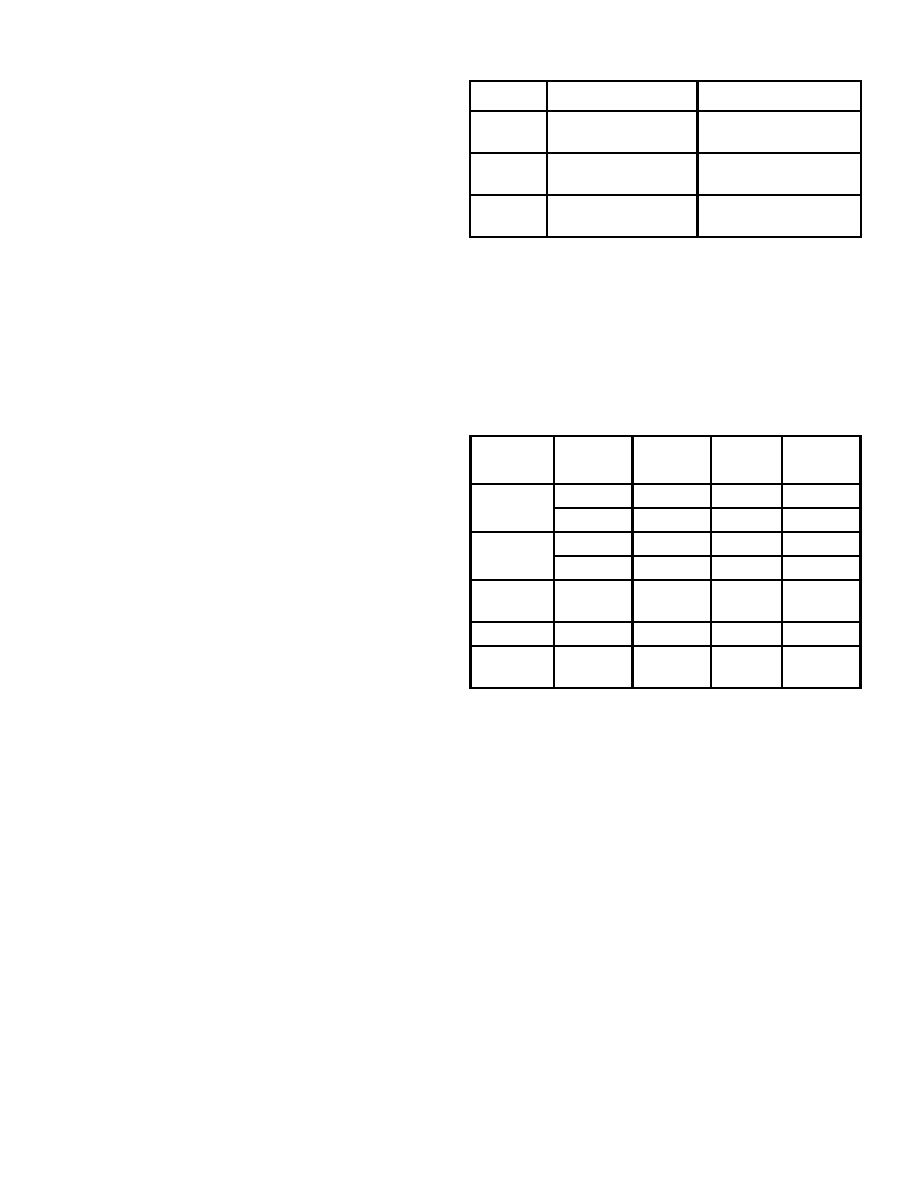

Table 3 – ALU Operations

Unit

F Pipe

M Pipe

Adder

add, sub

add, sub, data

address add

Logic

logic, moves, zero

shifts (nop)

logic, moves, zero

shifts (nop)

Shifter

non zero shift

non zero shift, store

align

Table 4 – Integer Multiply / Divide Operations

Opcode

Operand

Size

Latency

Repeat

Rate

Stall

Cycles

MULT/U,

MAD/U

16 bit

430

32 bit

540

MUL

16 bit

4

3

2

32 bit

543

DMULT,

DMULTU

any

980

DIV, DIVD

any

36

0

DDIV,

DDIVU

any

68

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ACT4445 | DATACOM, MIL-STD-1553 DATA BUS TRANSCEIVER, BCC64 |

| ACTS04KMSR-02 | ACT SERIES, HEX 1-INPUT INVERT GATE, CDFP14 |

| ACTS04DMSR-02 | ACT SERIES, HEX 1-INPUT INVERT GATE, CDIP14 |

| ACTS08DMSR | ACT SERIES, QUAD 2-INPUT AND GATE, CDIP14 |

| ACTS138HMSR-02 | ACT SERIES, OTHER DECODER/DRIVER, INVERTED OUTPUT, UUC16 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ACT7000SC | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:ACT 7000SC 64-Bit Superscaler Microprocessor |

| ACT-7000SC-150F17C | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:ACT 7000SC 64-Bit Superscaler Microprocessor |

| ACT-7000SC-150F17I | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:ACT 7000SC 64-Bit Superscaler Microprocessor |

| ACT-7000SC-150F17M | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:ACT 7000SC 64-Bit Superscaler Microprocessor |

| ACT-7000SC-150F17Q | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:ACT 7000SC 64-Bit Superscaler Microprocessor |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。