- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362038 > A8351601SERIES Bar Code Reader PDF資料下載

參數(shù)資料

| 型號: | A8351601SERIES |

| 英文描述: | Bar Code Reader |

| 中文描述: | 條碼閱讀器 |

| 文件頁數(shù): | 5/43頁 |

| 文件大?。?/td> | 413K |

| 代理商: | A8351601SERIES |

第1頁第2頁第3頁第4頁當前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁

A8351601 Series

PRELIMINARY (October, 2001, Version 0.5)

4

AMIC Technology, Inc.

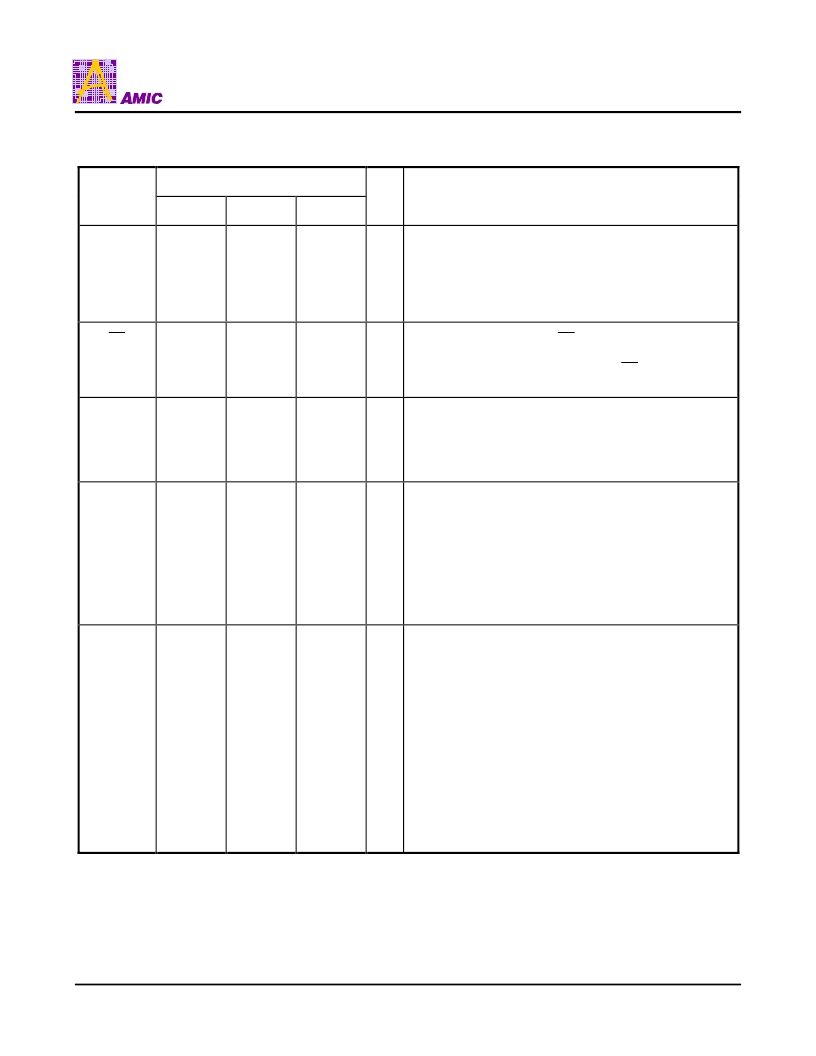

Pin Description

Pin No.

Symbol

P-DIP

PLCC

QFP

I/O

Description

ALE

30

33

27

O

Address Latch Enable:

Output pulse for latching the low

byte of the address during an address to the external

memory. In normal operation, ALE is emitted at a constant

rate of 1/6 the oscillator frequency, and can be used for

external timing or clocking. Note that one ALE pulse is

skipped during each access to external data memory.

EA

31

35

29

I

External Access enable:

EA

must be externally held low

to enable the device to fetch code from external program

memory locations 0000H to FFFFH. If

EA

is held high, the

device executes from internal program memory.

P0.0-P0.7

32-39

36-43

30-37

I/O

Port 0:

Port 0 is an 8-bit bidirectional I/O port with internal

pullups. Port 0 pins that have 1s written to them are pulled

high by the internal pullups and can be used as inputs. Port

0 is also the multiplexed low-order address and data bus

during accesses to external program and data memory.

1-8

2-9

40-44

I/O

Port 1:

Port 1 is an 8-bit bidirectional I/O port with internal

pullups. Port 1 pins that have 1s written to them are pulled

high by the internal pullups and can be used as inputs. As

inputs, Port 1 pins that are externally pulled low will source

current because of the internal pullups. (See DC

Characteristics: I

IL

).

The Port 1 output buffers can sink/source four TTL inputs.

T2 (P1.0):

Timer/Counter 2 external count input.

T2EX (P1.1):

Timer/Counter 2 trigger input.

1

2

2

3

40

41

I

I

P1.0-P1.7

P2.0-P2.7

21-28

24-31

18-25

I/O

Port 2:

Port 2 is an 8-bit bidirectional I/O port with internal

pullups. Port 2 pins that have 1s written to them are pulled

high by the internal pullups and can be used as inputs. As

inputs, Port 2 pins that are externally pulled low will source

current because of the internal pullups. (See DC

Characteristics: I

IL

).

Port 2 emits the high order address byte during fetches

from external program memory and during accesses to

external data memory that used 16-bit addresses (MOVX @

DPTR). In this application, Port 2 uses strong internal

pullups when emitting 1s. During accesses to external data

memory that use 8-bit addresses (MOVX @ Ri [i = 0, 1]),

Port 2 emits the contents of the P2 Special Function

Register.

Port 2 also receives the high-order bits and some control

signals during ROM verification.

相關PDF資料 |

PDF描述 |

|---|---|

| A8396BH | 16-Bit Microcontroller |

| C8395BH | Single buffer (open drain) |

| LC8395BH | 16-Bit Microcontroller |

| LN8396BH | 16-Bit Microcontroller |

| LP8395BH | 16-Bit Microcontroller |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| A83516-12 | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:8 Bit Microcontroller |

| A83516-24 | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:8 Bit Microcontroller |

| A83516-40 | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:8 Bit Microcontroller |

| A83516L-12 | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:8 Bit Microcontroller |

| A83516L-24 | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:8 Bit Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復。