- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25565 > 9EPRS475CGLF (INTEGRATED DEVICE TECHNOLOGY INC) PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF資料下載

參數(shù)資料

| 型號: | 9EPRS475CGLF |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘產(chǎn)生/分配 |

| 英文描述: | PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封裝: | 6.10 MM, 0.50 MM PITCH, ROHS COMPLIANT, MO-153, TSSOP-56 |

| 文件頁數(shù): | 8/20頁 |

| 文件大小: | 177K |

| 代理商: | 9EPRS475CGLF |

IDT

System Clock for Embedded AMDTM based Systems

1615B—04/26/10

9EPRS475

System Clock for Embedded AMDTM based Systems

16

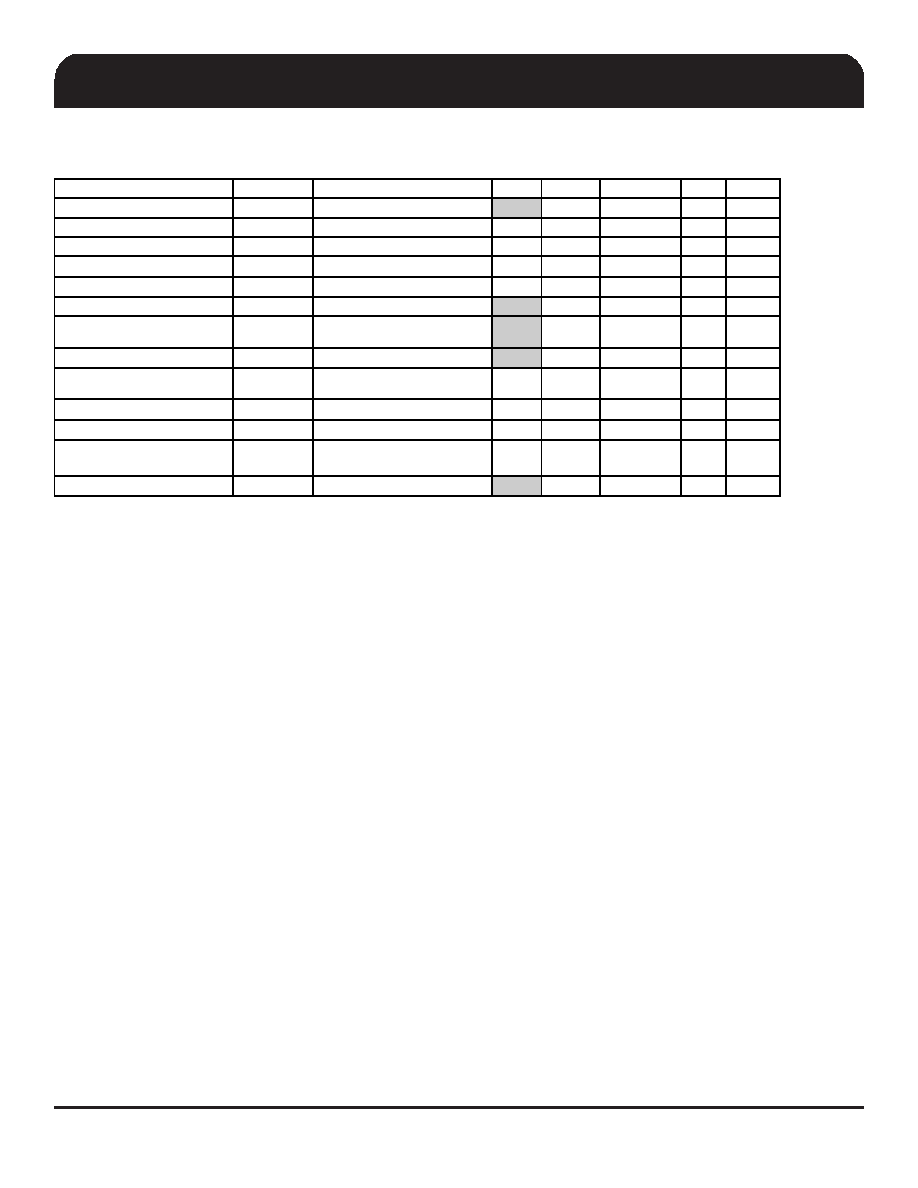

AC Electrical Characteristics - Low-Power DIF Outputs: CPUKG and HTT

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS NOTES

Crossing Point Variation

ΔV

CROSS

Single-ended Measurement

140

mV

1,2,5

Frequency

f

Spread Specturm On

198.8

200

MHz

1,3

Long Term Accuracy

ppm

Spread Specturm Off

-300

+300

ppm

1,11

Rising Edge Slew Rate

S

RISE

Differential Measurement

0.5

10

V/ns

1,4

Falling Edge Slew Rate

S

FALL

Differential Measurement

0.5

10

V/ns

1,4

Slew Rate Variation

t

SLVAR

Single-ended Measurement

20

%

1

CPU, DIF HTT Jitter - Cycle to

Cycle

CPUJ

C2C

Differential Measurement

150

ps

1,6

Accumulated Jitter

t

JACC

See Notes

1

ns

1,7

Peak to Peak Differential

Voltage

V

D(PK-PK)

Differential Measurement

400

2400

mV

1,8

Differential Voltage

V

D

Differential Measurement

200

1200

mV

1,9

Duty Cycle

D

CYC

Differential Measurement

45

55

%

1

Amplitude Variation

ΔV

D

Change in V

D DC cycle to cycle

-75

75

mV

1,10

CPU[1:0] Skew

CPU

SKEW10

Differential Measurement

100

ps

1

Notes on Electrical Characteristics:

Guaranteed by design and characterization, not 100% tested in production.

Minimum Frequency is a result of 0.5% down spread spectrum

6 Max difference of t

CYCLE between any two adjacent cycles.

7 Accumulated tjc.over a 10 s time period, measured with JIT2 TIE at 50ps interval.

8 VD(PK-PK) is the overall magnitude of the differential signal.

10 The difference in magnitude of two adjacent VD_DC measurements. VD_DC is the stable post overshoot and ring-back part of the signal.

11 All Long Term Accuracy and Clock Period specifications are guaranteed assuming that REFOUT is at 14.31818MHz

Single-ended measurement at crossing point. Value is maximum – minimum over all time. DC value of common mode is

not important due to the blocking cap.

5 Defined as the total variation of all crossing voltages of CLK rising and CLK# falling. Matching applies to rising edge rate of

CLK and falling edge of CLK#. It is measured using a +/-75mV window centered on the average cross point where CLK

meets CLK#.

Differential measurement through the range of ±100 mV, differential signal must remain monotonic and within slew rate

spec when crossing through this region.

9 VD(min) is the amplitude of the ring-back differential measurement, guaranteed by design, that ring-back will not cross

0V VD. VD(max) is the largest amplitude allowed.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 9EPRS475CGLFT | PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 9EPRS488CKLF | SPECIALTY MICROPROCESSOR CIRCUIT, PQCC72 |

| 9EPRS488CKLFT | SPECIALTY MICROPROCESSOR CIRCUIT, PQCC72 |

| 9EPRS525AGILF | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO56 |

| 9ERS3165BGILFT | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO64 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 9EPRS475CGLFT | 功能描述:實時時鐘 RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 總線接口:I2C 日期格式:DW:DM:M:Y 時間格式:HH:MM:SS RTC 存儲容量:64 B 電源電壓-最大:5.5 V 電源電壓-最小:1.8 V 最大工作溫度:+ 85 C 最小工作溫度: 安裝風(fēng)格:Through Hole 封裝 / 箱體:PDIP-8 封裝:Tube |

| 9EPRS488CKLF | 功能描述:時鐘合成器/抖動清除器 Embedded 72P CLK f/ AMD Based System RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 9EPRS488CKLFT | 功能描述:時鐘合成器/抖動清除器 Embedded 72P CLK f/ AMD Based System RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 9EPRS525AGILF | 功能描述:時鐘合成器/抖動清除器 EMBEDDED 56P CK505 COMPATIBLE RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 9EPRS525AGILFT | 功能描述:時鐘合成器/抖動清除器 EMBEDDED 56P CK505 COMPATIBLE RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。