- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25564 > 9DB423BFLF (INTEGRATED DEVICE TECHNOLOGY INC) 9DB SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 PDF資料下載

參數(shù)資料

| 型號: | 9DB423BFLF |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘及定時 |

| 英文描述: | 9DB SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 封裝: | 0.209 INCH, ROHS COMPLIANT, MO-150, SSOP-28 |

| 文件頁數(shù): | 17/19頁 |

| 文件大?。?/td> | 199K |

| 代理商: | 9DB423BFLF |

IDT

Four Output Differential Buffer for PCIe Gen 1, Gen 2 and QPI

1437 Rev D - 05/09/11

9DB423B

Four Output Differential Buffer for PCIe for Gen 1, Gen 2 and QPI

7

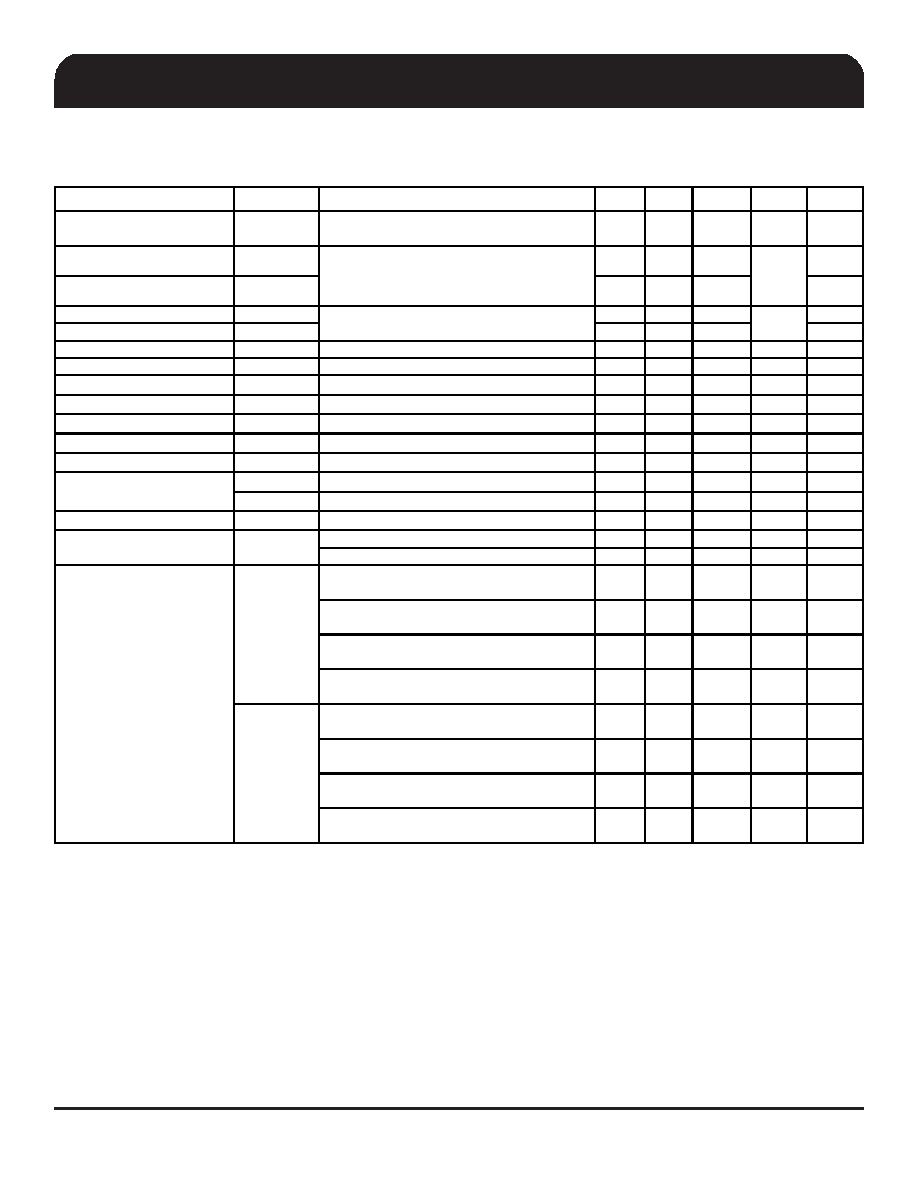

Electrical Characteristics - DIF 0.7V Current Mode Differential Pair

TA = 0 - 70°C; VDD = 3.3 V +/-5%; CL =2pF, RS=33, RP=49.9, RREF=475

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS NOTES

Current Source Output

Impedance

Zo

1

3000

Ω

1

Voltage High

VHigh

660

850

1,2

Voltage Low

VLow

-150

150

1,2

Max Voltage

Vovs

1150

1

Min Voltage

Vuds

-300

1

Crossing Voltage (abs)

Vcross(abs)

250

550

mV

1

Crossing Voltage (var)

d-Vcross

Variation of crossing over all edges

140

mV

1

Rise Time

tr

VOL = 0.175V, VOH = 0.525V

175

700

ps

1

Fall Time

tf

VOH = 0.525V VOL = 0.175V

175

700

ps

1

Rise Time Variation

d-tr

125

ps

1

Fall Time Variation

d-tf

125

ps

1

Duty Cycle

dt3

Measurement from differential wavefrom

45

55

%

1

tpdBYP

Bypass Mode, VT = 50%

2500

4500

ps

1

tpdPLL

PLL Mode VT = 50%

-250

250

ps

1

Skew, Output to Output

tsk3

VT = 50%

50

ps

1

PLL mode

50

ps1,3

Additive Jitter in Bypass Mode

50

ps1,3

PCIe Gen1 phase jitter

(Additive in Bypass Mode)

710

ps

(pk2pk)

1,4,5

PCIe Gen 2 Low Band phase jitter

(Additive in Bypass Mode)

00.1

ps

(rms)

1,4,5

PCIe Gen 2 High Band phase jitter

(Additive in Bypass Mode)

0.7

0.9

ps

(rms)

1,4,5

QPI phase jitter

(Additive in Bypass Mode)

0.16

ps

(rms)

1,5,6

PCIe Gen 1 phase jitter

37

86

ps

(pk2pk)

1,4,5

PCIe Gen 2 Low Band phase jitter

1.5

3

ps

(rms)

1,4,5

PCIe Gen 2 High Band phase jitter

2.7/

2.2

3.1

ps

(rms)

1,4,5,7

QPI phase jitter

0.28

0.5

ps

(rms)

1,5,6

1Guaranteed by design and characterization, not 100% tested in production.

2 I

REF = VDD/(3xRR). For RR = 475

Ω (1%), IREF = 2.32mA. IOH = 6 x IREF and VOH = 0.7V @ ZO=50Ω.

3 Measured from differential waveform

4 See http://www.pcisig.com for complete specs

5 Device driven by 932S421C or equivalent.

6 6.4Gb 12UI

7 First number is High Bandwidth Mode, second number is Low Bandwidth Mode

tjphasePLL

Skew, Input to Output

Statistical measurement on single ended

signal using oscilloscope math function.

mV

Measurement on single ended signal using

absolute value.

mV

Jitter, Cycle to cycle

tjcyc-cyc

tjphaseBYP

Jitter, Phase

相關PDF資料 |

PDF描述 |

|---|---|

| 9DB433AFILFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 9DB433AFLF | 9DB SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 9DB433AFLIFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 9DB433AGILFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 9DB433AFLFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 9DB423BFLFT | 功能描述:外圍驅(qū)動器與原件 - PCI 4 OUTPUT PCIE GEN2 BUFFER w/QPI RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| 9DB423BGLF | 功能描述:時鐘緩沖器 4 OUTPUT PCIE GEN2 BUFFER w/QPI RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9DB423BGLFT | 功能描述:時鐘緩沖器 4 OUTPUT PCIE GEN2 BUFFER w/QPI RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9DB433AFILF | 功能描述:時鐘緩沖器 4 OUTPUT PCIE GEN3 BUFFER RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9DB433AFILFT | 功能描述:時鐘緩沖器 4 OUTPUT PCIE GEN3 BUFFER RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。