- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄122717 > 935270050128 (NXP SEMICONDUCTORS) 4 CHANNEL(S), 5M bps, SERIAL COMM CONTROLLER, PQFP64 PDF資料下載

參數(shù)資料

| 型號(hào): | 935270050128 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 4 CHANNEL(S), 5M bps, SERIAL COMM CONTROLLER, PQFP64 |

| 封裝: | 10 X 10 MM, 1.40 MM HEIGHT, PLASTIC, MS-026, SOT-314-2, LQFP-64 |

| 文件頁數(shù): | 24/55頁 |

| 文件大小: | 706K |

| 代理商: | 935270050128 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當(dāng)前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁

Philips Semiconductors

SC16C654/654D

Quad UART with 64-byte FIFO and infrared (IrDA) encoder/decoder

Product data

Rev. 02 — 13 March 2003

30 of 52

9397 750 10985

Koninklijke Philips Electronics N.V. 2003. All rights reserved.

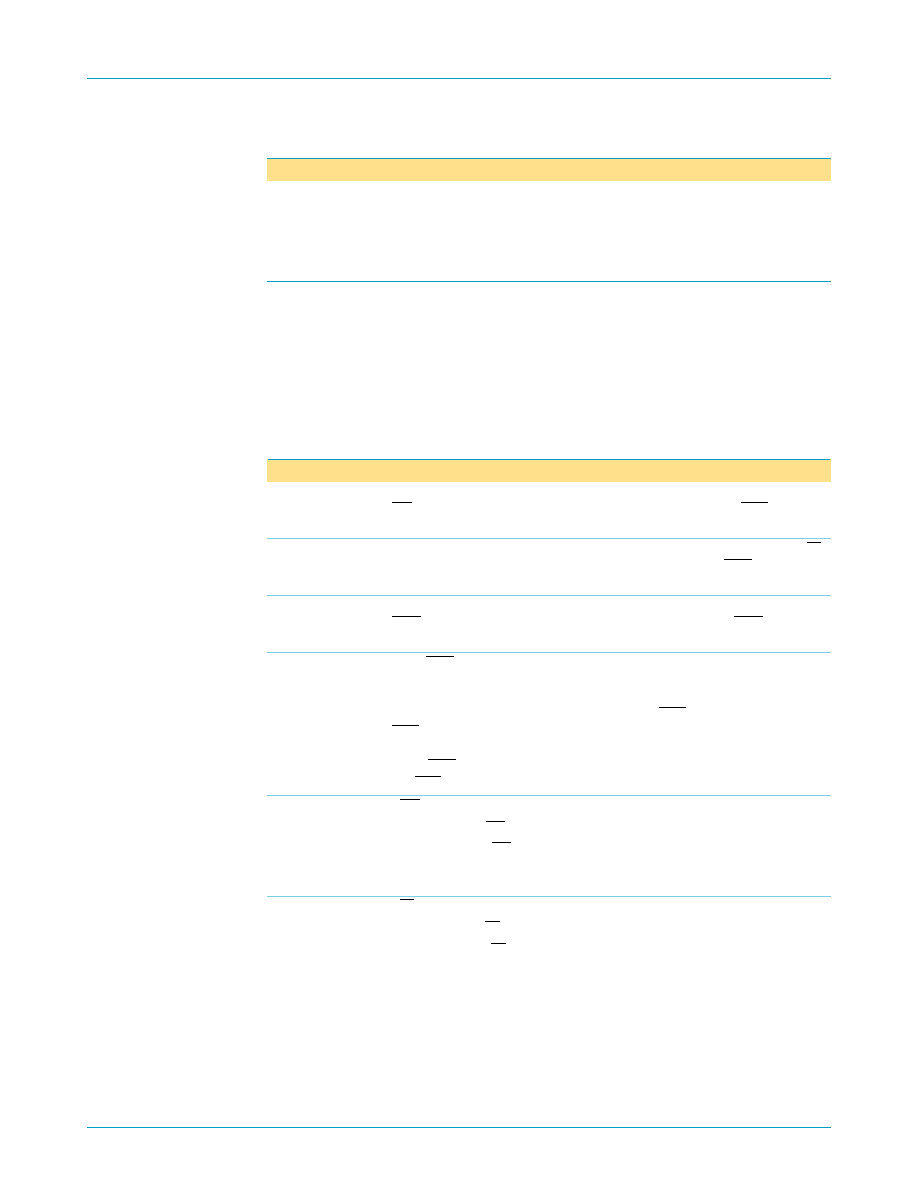

7.8 Modem Status Register (MSR)

This register provides the current state of the control interface signals from the

modem, or other peripheral device to which the SC16C654/654D is connected.

Four bits of this register are used to indicate the changed information. These bits are

set to a logic 1 whenever a control input from the modem changes state. These bits

are set to a logic 0 whenever the CPU reads this register.

0

LSR[0]

Receive data ready.

Logic 0 = No data in receive holding register or FIFO (normal default

condition).

Logic 1 = Data has been received and is saved in the receive holding

register or FIFO.

Table 20:

Line Status Register bits description…continued

Bit

Symbol

Description

Table 21:

Modem Status Register bits description

Bit

Symbol

Description

7

MSR[7]

CD (Active-HIGH, logical 1). Normally this bit is the complement of the

CD input. In the loop-back mode this bit is equivalent to the OP2 bit in the

MCR register.

6

MSR[6]

RI (Active-HIGH, logical 1). Normally this bit is the complement of the RI

input. In the loop-back mode this bit is equivalent to the OP1 bit in the

MCR register.

5

MSR[5]

DSR (Active-HIGH, logical 1). Normally this bit is the complement of the

DSR input. In loop-back mode this bit is equivalent to the DTR bit in the

MCR register.

4

MSR[4]

CTS. CTS functions as hardware ow control signal input if it is enabled

via EFR[7]. The transmit holding register ow control is enabled/disabled

by MSR[4]. Flow control (when enabled) allows starting and stopping the

transmissions based on the external modem CTS signal. A logic 1 at the

CTS pin will stop SC16C654/654D transmissions as soon as current

character has nished transmission. Normally MSR[4] is the complement

of the CTS input. However, in the loop-back mode, this bit is equivalent to

the RTS bit in the MCR register.

3

MSR[3]

CD [1]

Logic 0 = No CD change (normal default condition).

Logic1=The CD input to the SC16C654/654D has changed state

since the last time it was read. A modem Status Interrupt will be

generated.

2

MSR[2]

RI [1]

Logic 0 = No RI change (normal default condition).

Logic1=The RI input to the SC16C654/654D has changed from a

logic 0 to a logic 1. A modem Status Interrupt will be generated.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935269195118 | 8 I/O, PIA-GENERAL PURPOSE, PDSO16 |

| 935056380512 | 8 CHANNEL(S), 115.2K bps, SERIAL COMM CONTROLLER, PQCC84 |

| 932S203YGT | 133.3 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 935069310118 | I2C BUS CONTROLLER, PDSO20 |

| 9LRS3187BKLF | 133.33 MHz, PROC SPECIFIC CLOCK GENERATOR, PQCC32 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935270713557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC CHP |

| 935270792551 | 制造商:NXP Semiconductors 功能描述:IC BUFF DVR TRI-ST 16BIT 56VFBGA |

| 935270792557 | 制造商:NXP Semiconductors 功能描述:IC BUFF DVR TRI-ST 16BIT 56VFBGA |

| 935270793551 | 制造商:NXP Semiconductors 功能描述:IC BUS TRCVR 3-ST 16BIT 56VFBGA |

| 935270793557 | 制造商:NXP Semiconductors 功能描述:IC BUS TRCVR 3-ST 16BIT 56VFBGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。