- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24830 > 935264570557 (NXP SEMICONDUCTORS) 1 CHANNEL(S), SERIAL COMM CONTROLLER, PQFP80 PDF資料下載

參數(shù)資料

| 型號: | 935264570557 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 1 CHANNEL(S), SERIAL COMM CONTROLLER, PQFP80 |

| 封裝: | 12 X 12 MM, 1.40 MM HEIGHT, PLASTIC, MS-026, SOT-315-1, LQFP-80 |

| 文件頁數(shù): | 32/36頁 |

| 文件大小: | 145K |

| 代理商: | 935264570557 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁第35頁第36頁

2000 Nov 17

5

Philips Semiconductors

Preliminary specication

1394 SBP-2 link layer controller

SAA7356HL

6

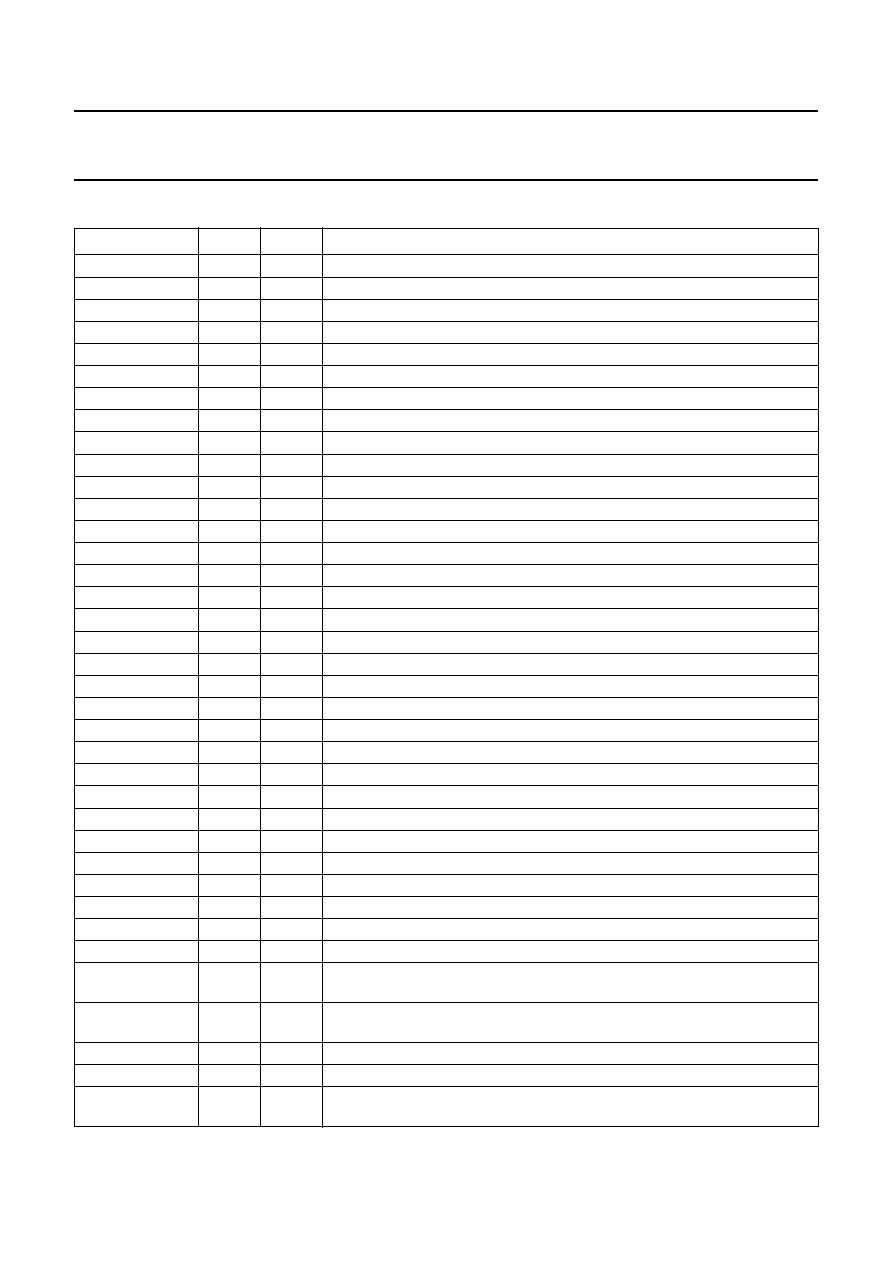

PIN CONFIGURATION

SYMBOL

PIN

TYPE(1)

DESCRIPTION

MICRO_ADDR[0]

1

I

microcontroller address input (bit 0); note 2

MICRO_ADDR[1]

2

I

microcontroller address input (bit 1); note 2

MICRO_ADDR[2]

3

I

microcontroller address input (bit 2); note 2

MICRO_ADDR[3]

4

I

microcontroller address input (bit 3); note 2

VDD1(P)

5

S

supply voltage 1 for periphery

VSS1(P)

6

S

ground 1 for periphery

MICRO_ADDR[4]

7

I

microcontroller address input (bit 4); note 2

MICRO_ADDR[5]

8

I

microcontroller address input (bit 5); note 2

MICRO_ADDR[6]

9

I

microcontroller address input (bit 6); note 2

MICRO_ADDR[7]

10

I

microcontroller address input (bit 7); note 2

VDD2(P)

11

S

supply voltage 2 for periphery

VSS2(P)

12

S

ground 2 for periphery

DMA_DATA[15]

13

I /O

DMA data input/output (bit 15); note 3

DMA_DATA[14]

14

I /O

DMA data input/output (bit 14); note 3

DMA_DATA[13]

15

I /O

DMA data input/output (bit 13); note 3

DMA_DATA[12]

16

I /O

DMA data input/output (bit 12); note 3

DMA_DATA[11]

17

I /O

DMA data input/output (bit 11); note 3

DMA_DATA[10]

18

I /O

DMA data input/output (bit 10); note 3

VDD1(C)

19

S

supply voltage 1 for core

VSS1(C)

20

S

ground 1 for core

DMA_DATA[9]

21

I /O

DMA data input/output (bit 9); note 3

DMA_DATA[8]

22

I /O

DMA data input/output (bit 8); note 3

DMA_DATA[7]

23

I /O

DMA data input/output (bit 7); note 3

DMA_DATA[6]

24

I /O

DMA data input/output (bit 6); note 3

DMA_DATA[5]

25

I /O

DMA data input/output (bit 5); note 3

DMA_DATA[4]

26

I /O

DMA data input/output (bit 4); note 3

DMA_DATA[3]

27

I /O

DMA data input/output (bit 3); note 3

DMA_DATA[2]

28

I /O

DMA data input/output (bit 2); note 3

VSS3(P)

29

S

ground 3 for periphery

VDD3(P)

30

S

supply voltage 3 for periphery

DMA_DATA[1]

31

I /O

DMA data input/output (bit 1); note 3

DMA_DATA[0]

32

I /O

DMA data input/output (bit 0); note 3

DMA_REQ

33

O

DMA request signal output in slave mode (acknowledge in master/ATA mode)

(may be congured for active HIGH or active LOW)

DMA_ACK

34

I

DMA acknowledge signal input in slave mode (request in master/ATA mode)

(may be congured for active HIGH or active LOW)

VSS2(C)

35

S

ground 2 for core

VDD2(C)

36

S

supply voltage 2 for core

DMA_READ

37

I /O

DMA read strobe input/output (may be congured for active HIGH or active

LOW)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 0803-7700-02 | Integrated VDSL Filter/Hybrid Solution |

| 935269451118 | 133 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 935269451112 | 133 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 0803-7700-03 | VDSL / PSTN CO Splitter |

| 935269471115 | 2.8 V FIXED POSITIVE LDO REGULATOR, 0.06 V DROPOUT, PDSO5 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

| 935269544557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-2US1-V1.3 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。