- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24767 > 935143850129 (NXP SEMICONDUCTORS) 2 CHANNEL(S), 1M bps, SERIAL COMM CONTROLLER, PDIP28 PDF資料下載

參數(shù)資料

| 型號(hào): | 935143850129 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, SERIAL COMM CONTROLLER, PDIP28 |

| 封裝: | 0.600 INCH, PLASTIC, MO-015AH, SOT-117-1, DIP-28 |

| 文件頁數(shù): | 32/34頁 |

| 文件大?。?/td> | 313K |

| 代理商: | 935143850129 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁

Philips Semiconductors

Product specification

SCN2681

Dual asynchronous receiver/transmitter (DUART)

1998 Sep 04

7

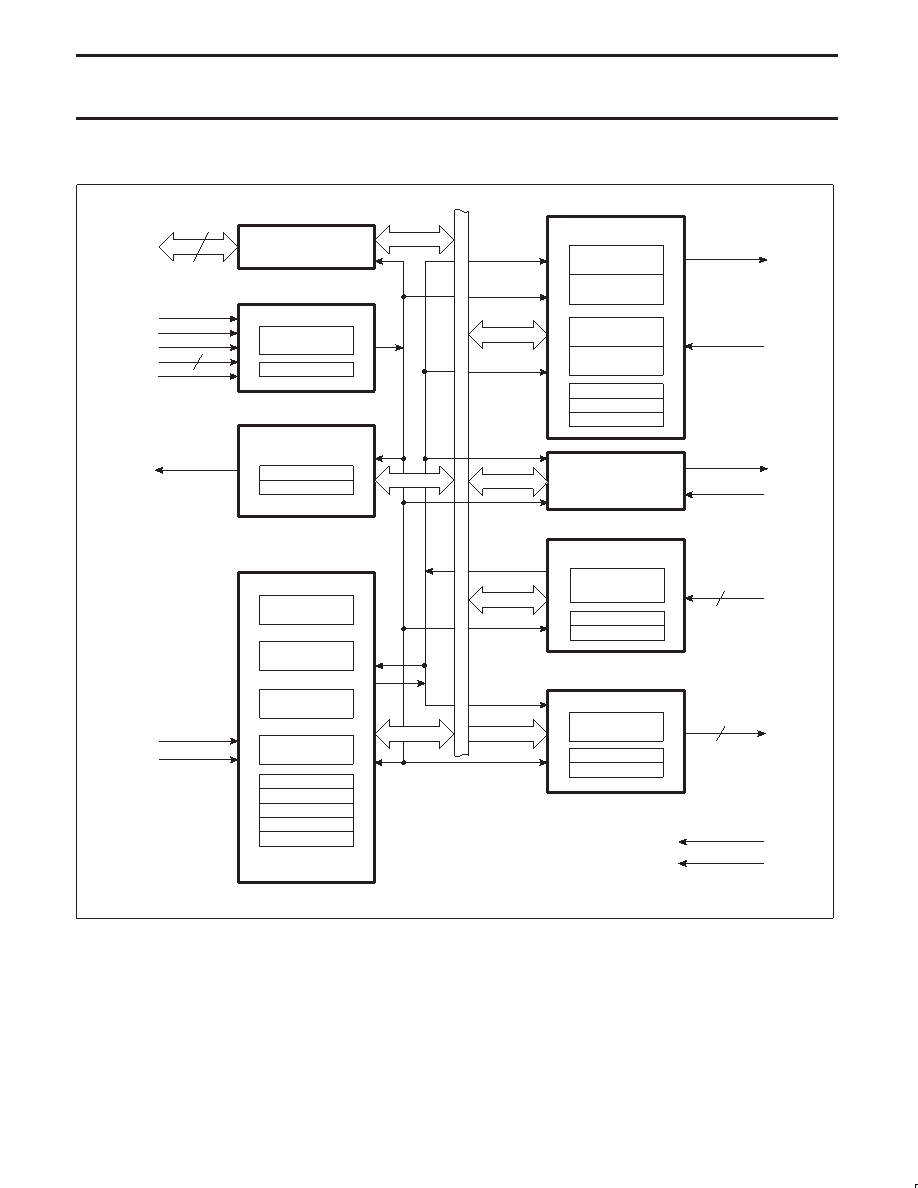

BLOCK DIAGRAM

8

D0–D7

RDN

WRN

CEN

A0–A3

RESET

INTRN

X1/CLK

X2

4

BUS BUFFER

OPERATION CONTROL

ADDRESS

DECODE

R/W CONTROL

INTERRUPT CONTROL

IMR

ISR

TIMING

BAUD RATE

GENERATOR

CLOCK

SELECTORS

COUNTER/

TIMER

XTAL OSC

CSRA

CSRB

ACR

CTUR

CHANNEL A

TRANSMIT

HOLDING REG

TRANSMIT

SHIFT REGISTER

RECEIVE

HOLDING REG (3)

RECEIVE

SHIFT REGISTER

MRA1, 2

CRA

SRA

INPUT PORT

CHANGE OF

STATE

DETECTORS (4)

OUTPUT PORT

FUNCTION

SELECT LOGIC

OPCR

TxDA

RxDA

IP0-IP6

OP0-OP7

VCC

GND

CONTROL

TIMING

INTERNAL

DA

T

ABUS

CHANNEL B

(AS ABOVE)

IPCR

ACR

OPR

CTLR

RxDB

TxDB

8

7

SD00085

Figure 2. Block Diagram

BLOCK DIAGRAM

The SCN2681 DUART consists of the following eight major sections:

data bus buffer, operation control, interrupt control, timing,

communications Channels A and B, input port and output port.

Refer to the block diagram.

Data Bus Buffer

The data bus buffer provides the interface between the external and

internal data buses. It is controlled by the operation control block to

allow read and write operations to take place between the controlling

CPU and the DUART.

Operation Control

The operation control logic receives operation commands from the

CPU and generates appropriate signals to internal sections to

control device operation. It contains address decoding and read and

write circuits to permit communications with the microprocessor via

the data bus buffer.

Interrupt Control

A single active-Low interrupt output (INTRN) is provided which is

activated upon the occurrence of any of eight internal events.

Associated with the interrupt system are the Interrupt Mask Register

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935026920512 | 2 CHANNEL(S), 1M bps, SERIAL COMM CONTROLLER, PQCC44 |

| 933662770129 | 2 CHANNEL(S), 1M bps, SERIAL COMM CONTROLLER, PDIP28 |

| 935143850112 | 2 CHANNEL(S), 1M bps, SERIAL COMM CONTROLLER, PDIP28 |

| 0642560000 | 24 A, STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

| 0642760000 | 10 A, MODULAR TERMINAL BLOCK, 1 ROW, 2 DECKS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935144620510-T1O | 功能描述:硅電容器 WireBoundSiliconCap 10nF 0303 BV50 Au RoHS:否 制造商:IPDiA 電容:1 uF 容差:15 % 電壓額定值:5 V 溫度系數(shù):0.5 % 工作溫度范圍:- 55 C to + 150 C 封裝 / 箱體:1206 外殼高度:0.4 mm 系列:HSSC427.xxx 類型:1206 High Stability Silicon Capacitor |

| 935144620510-T3O | 功能描述:硅電容器 WireBoundSiliconCap 10nF 0303 BV50 Au RoHS:否 制造商:IPDiA 電容:1 uF 容差:15 % 電壓額定值:5 V 溫度系數(shù):0.5 % 工作溫度范圍:- 55 C to + 150 C 封裝 / 箱體:1206 外殼高度:0.4 mm 系列:HSSC427.xxx 類型:1206 High Stability Silicon Capacitor |

| 935145620510-T1O | 功能描述:硅電容器 WireBoundSiliconCap 10nF 0303 BV50 Au RoHS:否 制造商:IPDiA 電容:1 uF 容差:15 % 電壓額定值:5 V 溫度系數(shù):0.5 % 工作溫度范圍:- 55 C to + 150 C 封裝 / 箱體:1206 外殼高度:0.4 mm 系列:HSSC427.xxx 類型:1206 High Stability Silicon Capacitor |

| 935145620510-T3O | 功能描述:硅電容器 WireBoundSiliconCap 10nF 0303 BV50 Au RoHS:否 制造商:IPDiA 電容:1 uF 容差:15 % 電壓額定值:5 V 溫度系數(shù):0.5 % 工作溫度范圍:- 55 C to + 150 C 封裝 / 箱體:1206 外殼高度:0.4 mm 系列:HSSC427.xxx 類型:1206 High Stability Silicon Capacitor |

| 93515-091000 | 制造商:FCI 功能描述:PCMCIA T2 I/O RECEP 9POS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。