- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄68813 > 73S8010C-IM/F (MAXIM INTEGRATED PRODUCTS INC) SPECIALTY ANALOG CIRCUIT, QCC32 PDF資料下載

參數(shù)資料

| 型號: | 73S8010C-IM/F |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類: | 模擬信號調理 |

| 英文描述: | SPECIALTY ANALOG CIRCUIT, QCC32 |

| 封裝: | 5 X 5 MM, LEAD FREE, QFN-32 |

| 文件頁數(shù): | 6/27頁 |

| 文件大小: | 348K |

| 代理商: | 73S8010C-IM/F |

第1頁第2頁第3頁第4頁第5頁當前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁

73S8010C Data Sheet

DS_8010C_024

14

Rev. 1.5

A power-on-reset (POR) event will reset all of the control and status registers to their default states. A VDD fault

event does not reset these registers, but it will signal an interrupt condition and by the action of the timer that

creates interval “t1,” will not clear the interrupt until VDD is valid for at least the t1 time. The VDD fault can be

considered valid for VDD as low as 1.5 to 1.8 volts. At the lower range of the VDD fault, POR will be asserted.

11 Warm Reset

The 73S8010C automatically asserts a warm reset to the card when instructed through bit 1 of the I

2C Control

register (Warm Reset bit). The warm reset length is automatically defined as 42,000 card clock cycles. The bit

Warm Reset is automatically reset when the card starts answering or when the card is declared mute.

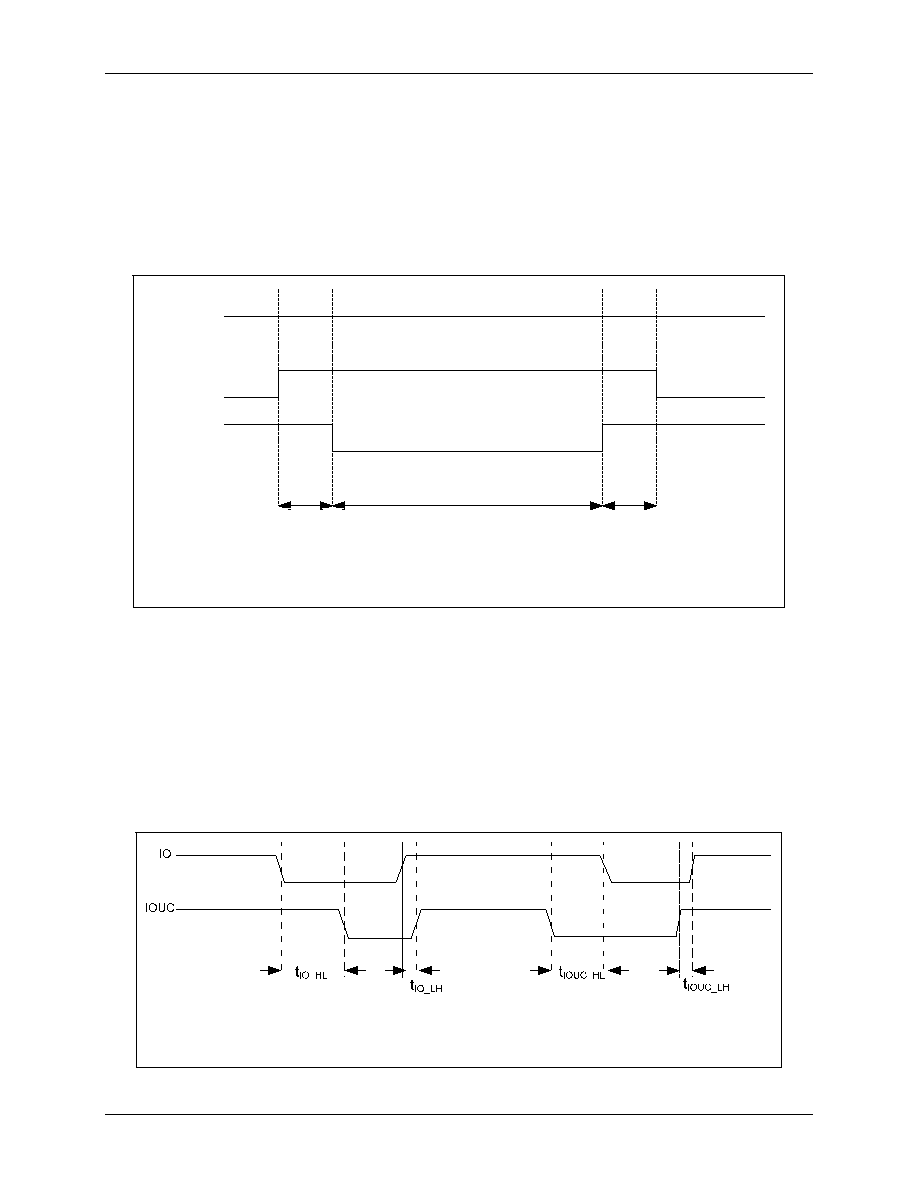

Figure 9: Warm Reset operation

12 I/O Timing

The states of the I/O, AUX1, and AUX2 pins are low after power on reset and they are high when the

activation sequencer turns on the I/O reception state. See Section 8 Activation Sequence for more

details on when the I/O reception is enabled.

The states of I/OUC, AUX1UC, and AUX2UC are high after power on reset. When the control I/O enable

bit (bit 7 of the Control register) is set, the first I/O line on which a falling edge is detected becomes the

input I/O line and the other becomes the output I/O line. When the input I/O line rising edge is detected

then both I/O lines return to their neutral state. The delay between the I/O signals is shown in Figure 10.

Figure 10: I/O Timing

Warm Reset

(bit 1)

RST

t1

t2

t3

IO

t1 > 1.5 s, Warm Reset Starts

t2 = 42000 card clock cycles, End of Warm Reset

t3 = Resets Warm Reset bit 1 when detected ATR or Mute

Delay from I/O to I/OUC:

tIO_HL = 100 ns

tIO_LH = 25 ns

Delay from I/OUC to I/O:

tI/OUC_HL = 100 ns tI/OUC_LH = 25 ns

相關PDF資料 |

PDF描述 |

|---|---|

| 73S8010C-IL | SPECIALTY ANALOG CIRCUIT, PDSO28 |

| 73S8010C-IMR | SPECIALTY ANALOG CIRCUIT, QCC32 |

| 73S8010C-IL | SPECIALTY ANALOG CIRCUIT, PDSO28 |

| 73S8010C-IM | SPECIALTY ANALOG CIRCUIT, QCC32 |

| 73S8010C-IM | SPECIALTY ANALOG CIRCUIT, QCC32 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 73S8010C-IMR/F | 功能描述:I2C 接口集成電路 Smart Card Interface ISO7816-3 & EVM4.0 RoHS:否 制造商:NXP Semiconductors 電源電壓-最大:5.5 V 電源電壓-最小:2.3 V 最大工作頻率:400 KHz 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-16 |

| 73S8010C-IMR/F1 | 功能描述:I2C 接口集成電路 RoHS:否 制造商:NXP Semiconductors 電源電壓-最大:5.5 V 電源電壓-最小:2.3 V 最大工作頻率:400 KHz 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-16 |

| 73S8010C-IMR/F2 | 功能描述:I2C 接口集成電路 RoHS:否 制造商:NXP Semiconductors 電源電壓-最大:5.5 V 電源電壓-最小:2.3 V 最大工作頻率:400 KHz 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-16 |

| 73S8010R | 制造商:TERIDIAN 制造商全稱:TERIDIAN 功能描述:Low Cost Smart Card Interface |

| 73S8010R-DB | 功能描述:界面開發(fā)工具 73S8010R Demo Brd RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

發(fā)布緊急采購,3分鐘左右您將得到回復。