- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄298480 > 70V3319S133BCGI (INTEGRATED DEVICE TECHNOLOGY INC) 256K X 18 DUAL-PORT SRAM, 4.2 ns, CBGA256 PDF資料下載

參數(shù)資料

| 型號: | 70V3319S133BCGI |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | SRAM |

| 英文描述: | 256K X 18 DUAL-PORT SRAM, 4.2 ns, CBGA256 |

| 封裝: | 17 X 17 MM X 1.4 MM, 1 MM PITCH, GREEN, BGA-256 |

| 文件頁數(shù): | 3/23頁 |

| 文件大?。?/td> | 222K |

| 代理商: | 70V3319S133BCGI |

6.42

IDT70V3319/99S

High-Speed 3.3V 256/128K x 18 Dual-Port Synchronous Static RAM

Industrial and Commercial Temperature Ranges

11

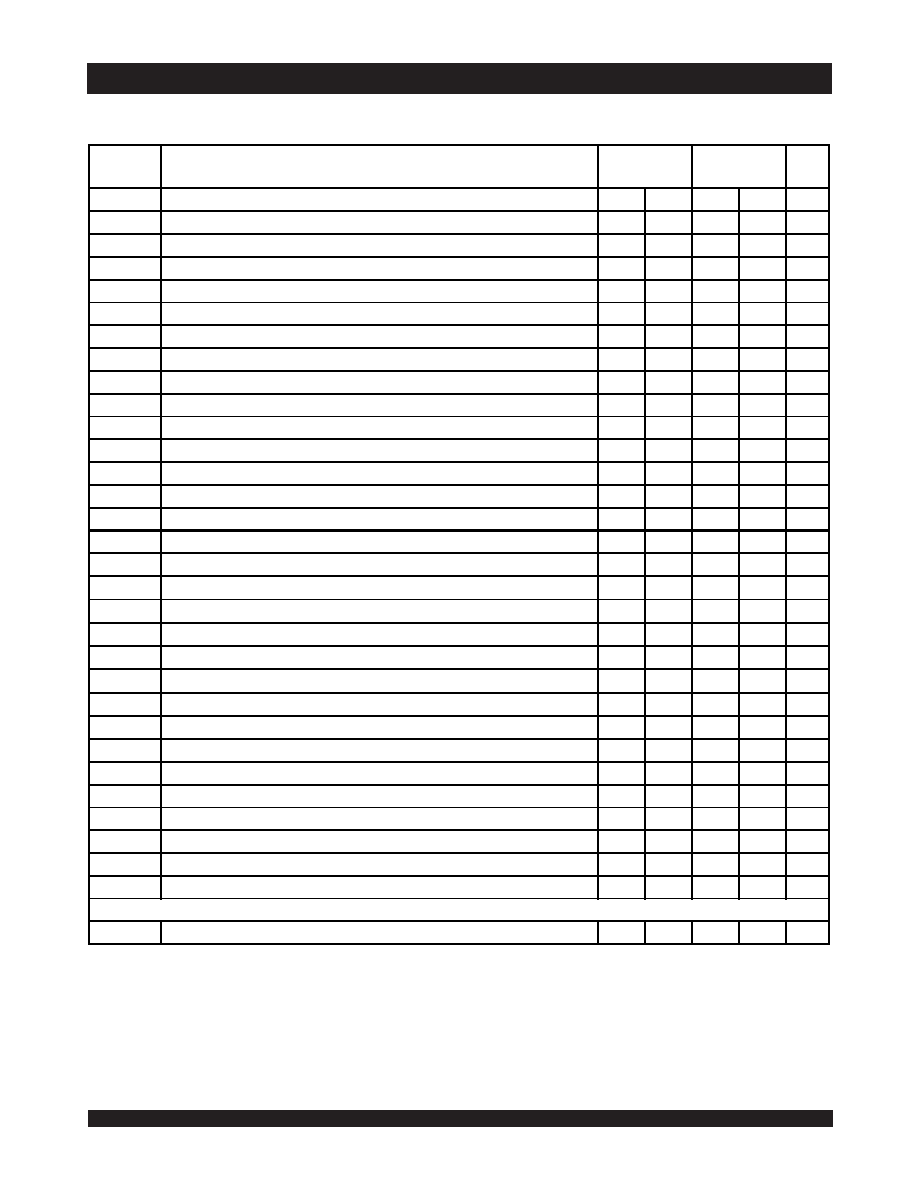

AC Electrical Characteristics Over the Operating Temperature Range

(Read and Write Cycle Timing)(2,3) (VDD = 3.3V ± 150mV, TA = 0°C to +70°C)

NOTES:

1. The Pipelined output parameters (tCYC2, tCD2) apply to either or both left and right ports when

FT/PIPEX = VIH. Flow-through parameters (tCYC1, tCD1) apply when

FT/PIPE = VIL for that port.

2. All input signals are synchronous with respect to the clock except for the asynchronous Output Enable (

OE) and FT/PIPE. FT/PIPE should be treated as a

DC signal, i.e. steady state during operation.

3. These values are valid for either level of VDDQ (3.3V/2.5V). See page 5 for details on selecting the desired operating voltage levels for each port.

70V3319/99S166

Com'l Only

70V3319/99S133

Com'l

& Ind

Symbol

Parameter

Min.

Max.

Min.

Max.

Unit

tCYC1

Clock Cycle Time (Flow-Through)

(1)

20

____

25

____

ns

tCYC2

Clock Cycle Time (Pipelined)(1)

6

____

7.5

____

ns

tCH1

Clock High Time (Flow-Through)(1)

6

____

7

____

ns

tCL1

Clock Low Time (Flow-Through)

(1)

6

____

7

____

ns

tCH2

Clock High Time (Pipelined)(2)

2.1

____

2.6

____

ns

tCL2

Clock Low Time (Pipelined)

(1)

2.1

____

2.6

____

ns

tSA

Address Setup Time

1.7

____

1.8

____

ns

tHA

Address Hold Time

0.5

____

0.5

____

ns

tSC

Chip Enable Setup Time

1.7

____

1.8

____

ns

tHC

Chip Enable Hold Time

0.5

____

0.5

____

ns

tSB

Byte Enable Setup Time

1.7

____

1.8

____

ns

tHB

Byte Enable Hold Time

0.5

____

0.5

____

ns

tSW

R/W Setup Time

1.7

____

1.8

____

ns

tHW

R/W Hold Time

0.5

____

0.5

____

ns

tSD

Input Data Setup Time

1.7

____

1.8

____

ns

tHD

Input Data Hold Time

0.5

____

0.5

____

ns

tSAD

ADS Setup Time

1.7

____

1.8

____

ns

tHAD

ADS Hold Time

0.5

____

0.5

____

ns

tSCN

CNTEN Setup Time

1.7

____

1.8

____

ns

tHCN

CNTEN Hold Time

0.5

____

0.5

____

ns

tSRPT

REPEAT Setup Time

1.7

____

1.8

____

ns

tHRPT

REPEAT Hold Time

0.5

____

0.5

____

ns

tOE

Output Enable to Data Valid

____

4.0

____

4.2

ns

tOLZ

Output Enable to Output Low-Z

1

____

1

____

ns

tOHZ

Output Enable to Output High-Z

1

3.6

1

4.2

ns

tCD1

Clock to Data Valid (Flow-Through)(1)

____

12

____

15

ns

tCD2

Clock to Data Valid (Pipelined)

(1)

____

3.6

____

4.2

ns

tDC

Data Output Hold After Clock High

1

____

1

____

ns

tCKHZ

Clock High to Output High-Z

1

3

1

3

ns

tCKLZ

Clock High to Output Low-Z

1

____

1

____

ns

Port-to-Port Delay

tCO

Clock-to-Clock Offset

5

____

6

____

ns

5623 tbl 11

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 70V9389L9PRFI8 | 64K X 18 DUAL-PORT SRAM, 20 ns, PQFP128 |

| IDT70V9289L9PRF8 | 64K X 16 DUAL-PORT SRAM, 20 ns, PQFP128 |

| 710026-3 | 25 mm2, COPPER ALLOY, TIN FINISH, WIRE TERMINAL |

| 710027-5 | 35 mm2, COPPER ALLOY, TIN FINISH, WIRE TERMINAL |

| 710027-2 | 35 mm2, COPPER ALLOY, TIN FINISH, WIRE TERMINAL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 70V3319S133BCI | 功能描述:靜態(tài)隨機(jī)存取存儲器 256Kx18 STD-PWR 3.3V SYNC DUAL-PORT RAM RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| 70V3319S133BCI8 | 制造商:Integrated Device Technology Inc 功能描述:SRAM Chip Sync Dual 3.3V 4.5M-Bit 256K x 18 15ns/4.2ns 256-Pin CABGA T/R 制造商:Integrated Device Technology Inc 功能描述:SRAM SYNC DUAL 3.3V 4MBIT 256KX18 15NS/4.2NS 256BGA - Tape and Reel 制造商:Integrated Device Technology Inc 功能描述:256Kx18 STD-PWR 3.3V SYNC DUAL-PORT RAM |

| 70V3319S133BF | 功能描述:靜態(tài)隨機(jī)存取存儲器 256Kx18 STD-PWR 3.3V SYNC DUAL-PORT RAM RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| 70V3319S133BF8 | 制造商:Integrated Device Technology Inc 功能描述:SRAM Chip Sync Dual 3.3V 4.5M-Bit 256K x 18 15ns/4.2ns 208-Pin CABGA T/R 制造商:Integrated Device Technology Inc 功能描述:SRAM SYNC DUAL 3.3V 4MBIT 256KX18 15NS/4.2NS 208CABGA - Tape and Reel 制造商:Integrated Device Technology Inc 功能描述:256Kx18 STD-PWR 3.3V SYNC DUAL-PORT RAM |

| 70V3319S133BFI | 制造商:Integrated Device Technology Inc 功能描述:SRAM Chip Sync Dual 3.3V 4.5M-Bit 256K x 18 15ns/4.2ns 208-Pin CABGA 制造商:Integrated Device Technology Inc 功能描述:SRAM Chip Sync Dual 3.3V 4.5M-Bit 256K x 18 15ns/4.2ns 208-Pin CABGA Tray 制造商:Integrated Device Technology Inc 功能描述:SRAM SYNC DUAL 3.3V 4MBIT 256KX18 15NS/4.2NS 208CABGA - Rail/Tube 制造商:Integrated Device Technology Inc 功能描述:256Kx18 STD-PWR 3.3V SYNC DUAL-PORT RAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。