- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67325 > 5962-8768901VA (VISHAY SILICONIX) 8-CHANNEL, SGL ENDED MULTIPLEXER, CDIP18 PDF資料下載

參數(shù)資料

| 型號(hào): | 5962-8768901VA |

| 廠商: | VISHAY SILICONIX |

| 元件分類: | 多路復(fù)用及模擬開關(guān) |

| 英文描述: | 8-CHANNEL, SGL ENDED MULTIPLEXER, CDIP18 |

| 封裝: | CERAMIC, DIP-18 |

| 文件頁(yè)數(shù): | 8/12頁(yè) |

| 文件大?。?/td> | 170K |

| 代理商: | 5962-8768901VA |

Document Number: 70068

S11-1029–Rev. D, 23-May-11

www.vishay.com

5

Vishay Siliconix

DG528, DG529

This document is subject to change without notice.

THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

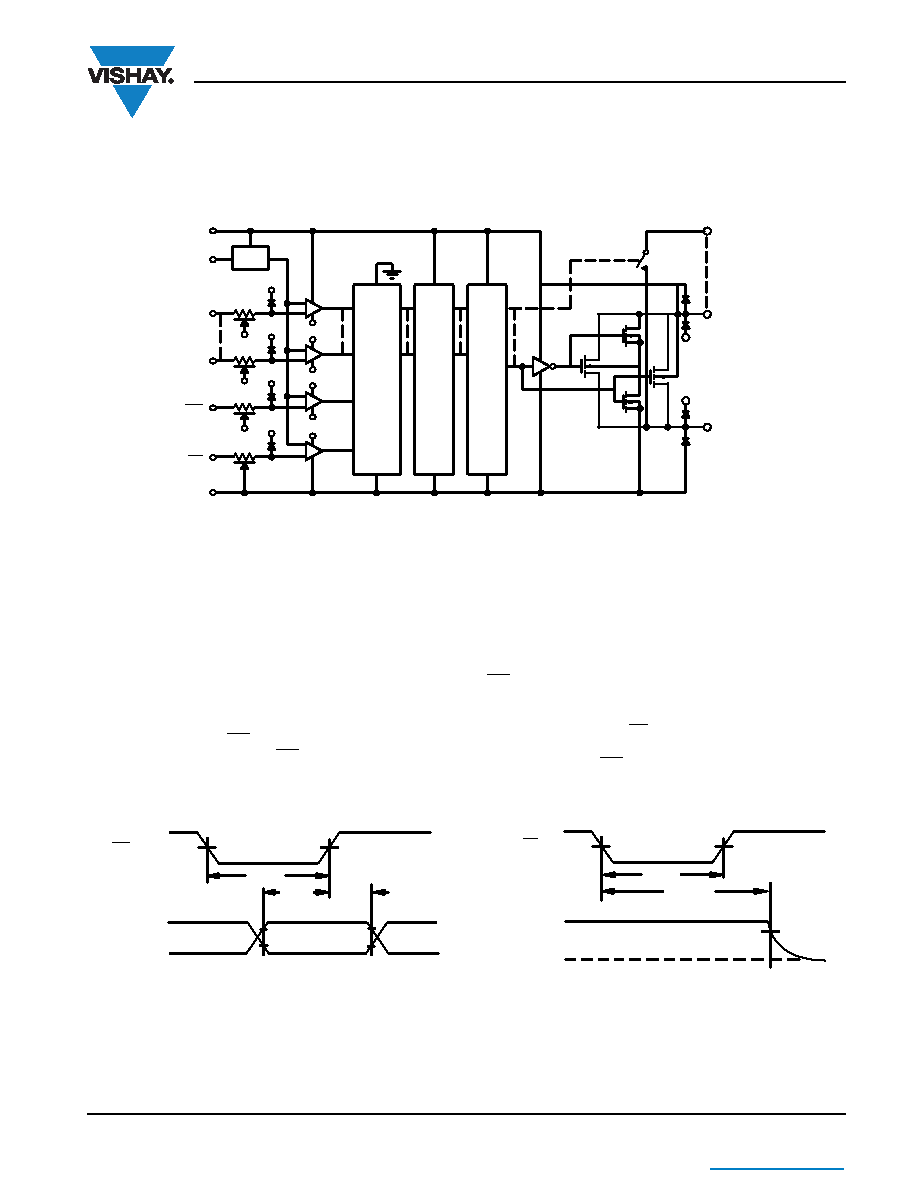

SCHEMATIC DIAGRAM (TYPICAL CHANNEL)

DETAILED DESCRIPTION

The internal structure of the DG528/DG529 includes a 5-V

logic interface with input protection circuitry followed by a

latch, level shifter, decoder and finally the switch constructed

with parallel n- and p-channel MOSFETs (see Figure 1).

The logic interface circuit compares the TTL input signal

against a TTL threshold reference voltage. The output of the

comparator feeds the data input of a D type latch. The level

sensitive D latch continuously places the DX input signal on

the QX output when the WR input is low, resulting in transpar-

ent latch operation. As soon as WR returns high, the latches

hold the data last present on the DX input, subject to the mini-

mum input timing requirements.

Following the latches the QX signals are level shifted and

decoded to provide proper drive levels for the CMOS

switches. This level shifting insures full on/off switch operation

for any analog signal present between the V+ and V- supply

rails.

The EN pin is used to enable the address latches during the

WR pulse. It can be hard-wired to the logic supply or to V+ if

one of the channels will always be used (except during a reset)

or it can be tied to address decoding circuitry for memory

mapped operation. The RS pin is used as a master reset. All

latches are cleared regardless of the state of any other latch

or control line. The WR pin is used to transfer the state of the

address control lines to their latches, except during a reset or

when EN is low (see Truth Tables).

Figure 1.

V+

Latches

EN

CLK

RESET

AX

WR

RS

VREF

DO

Dn

QO

Qn

Level

Shift

V+

V-

GND

V-

V+

D

V-

V+

Decode

S1

V-

V+

V-

V+

Sn

Figure 2.

3 V

0

3 V

0

50 %

80 %

EN

tW

tS

tH

WR

A0, A1, (A2)

Figure 3.

3 V

0

50 %

tRS

tOFF (RS)

RS

80 %

VO

Switch

Output

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 5962-87700012A | PARALLEL, 8 BITS INPUT LOADING, 8-BIT DAC, CQCC20 |

| 5962-8770001EA | PARALLEL, 8 BITS INPUT LOADING, 8-BIT DAC, CDIP16 |

| 5962-8770002EX | PARALLEL, 8 BITS INPUT LOADING, 8-BIT DAC, CDIP16 |

| 5962-8770003EX | PARALLEL, 8 BITS INPUT LOADING, 8-BIT DAC, CDIP16 |

| 5962-8770101RX | DUAL, PARALLEL, 8 BITS INPUT LOADING, 8-BIT DAC, CDIP20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 5962-8769002RA | 制造商:Advanced Micro Devices 功能描述: 制造商: 功能描述: 制造商:undefined 功能描述: |

| 5962-8769002SA | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| 5962-87692012A | 制造商:National Semiconductor Corporation 功能描述:Multiplexer 1-Element CMOS 3-ST 8-IN 20-Pin CLLCC 制造商:QP Semiconductor 功能描述:Multiplexer 1-Element CMOS 3-ST 8-IN 20-Pin CLLCC |

| 59628769201EA | 制造商:Texas Instruments 功能描述:54AC251DMQB |

| 5962-8769201EA | 制造商:QP Semiconductor 功能描述:MULTIPLEXER 1-ELEMENT CMOS 3-ST 8-IN 16-PIN CDIP |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。