- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67325 > 5962-8768901VA (VISHAY SILICONIX) 8-CHANNEL, SGL ENDED MULTIPLEXER, CDIP18 PDF資料下載

參數(shù)資料

| 型號: | 5962-8768901VA |

| 廠商: | VISHAY SILICONIX |

| 元件分類: | 多路復用及模擬開關 |

| 英文描述: | 8-CHANNEL, SGL ENDED MULTIPLEXER, CDIP18 |

| 封裝: | CERAMIC, DIP-18 |

| 文件頁數(shù): | 12/12頁 |

| 文件大小: | 170K |

| 代理商: | 5962-8768901VA |

DG528, DG529

Vishay General Semiconductor

Document Number: 70068

S11-1029–Rev. D, 23-May-11

www.vishay.com

9

This document is subject to change without notice.

THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

Notes:

a. Application Hints are for DESIGN AID ONLY, not guaranteed and not subject to production testing.

b. Electrical Parameter Chart based on V+ = 15 V, V- = - 15 V, VR = GND.

c. Operation below ± 8 V is not recommended.

The DG528/DG529 minimize the amount of interface hard-

ware between a microprocessor system bus and the analog

system being controlled or measured. The internal TTL com-

patible latches give these multiplexers write-only memory, that

is, they can be programmed to stay in a particular switch state

(e.g., switch 1 on) until the microprocessor determines it is

necessary to turn different switches on or turn all switches off

(see Figure 9).

The input latches become transparent when WR is held low;

therefore, these multiplexers operate by direct command of

the coded switch state on A2, A1, A0. In this mode the DG528

is identical to the popular DG508A. The same is true of the

DG529 versus the popular DG509A.

During system power-up, RS would be low, maintaining all

eight switches in the off state. After RS returned high the

DG528 maintains all switches in the off state. When the sys-

tem program performs a write operation to the address as-

signed to the DG528, the address decoder provides a CS

active low signal which is gated with the WRITE (WR) control

signal. At this time the data on the DATA BUS (that will deter-

mine which switch to close) is stabilizing. When the WR signal

returns to the high state, (positive edge) the input latches of

the DG528 save the data from the DATA BUS. The coded in-

formation in the A0, A1, A2 and EN latches is decoded and the

appropriate switch is turned on.

The EN latch allows all switches to be turned off under pro-

gram control. This becomes useful when two or more DG528s

are cascaded to build 16-line and larger multiplexers.

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Tech-

nology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability

data, see http://www.vishay.com/ppg?70068.

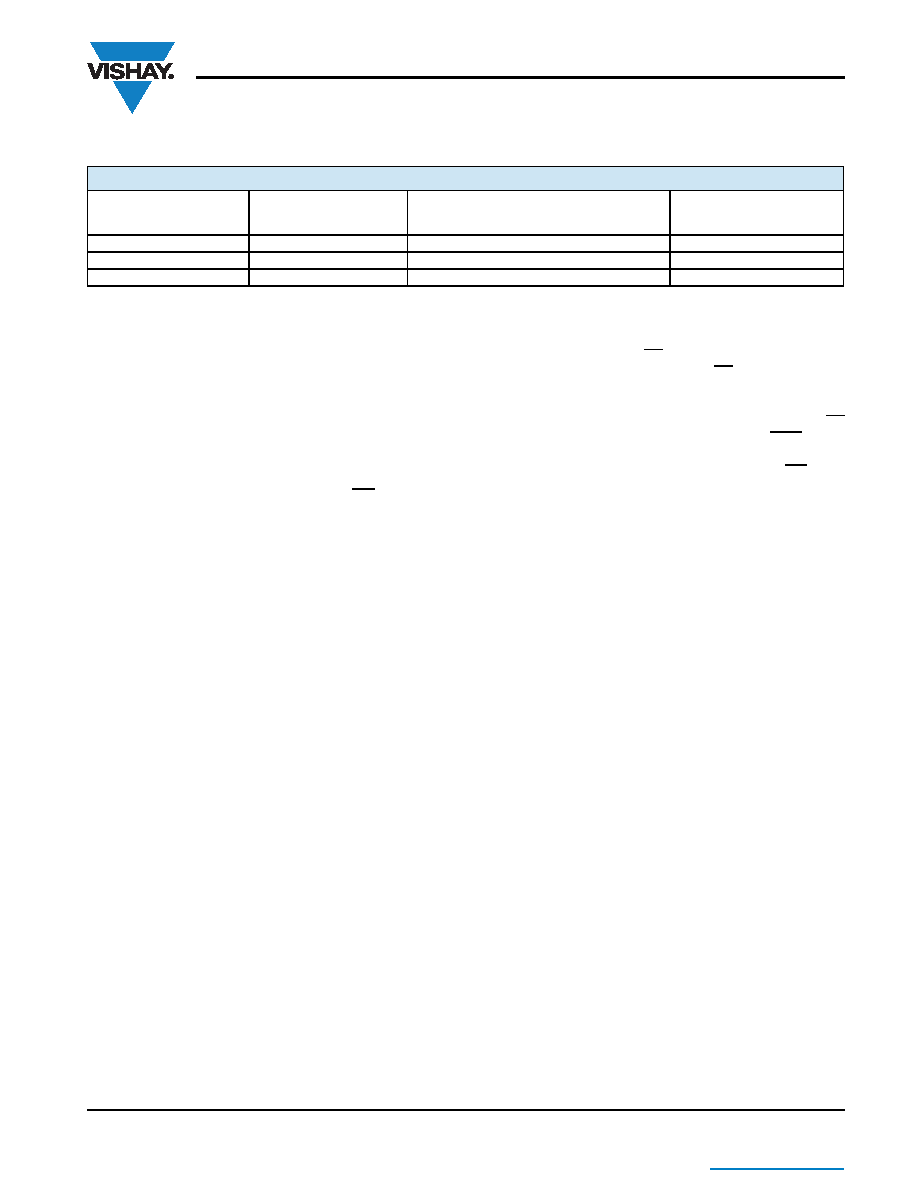

APPLICATION HINTSa

V+

Positive Supply Voltage

(V)

V-

Negative Supply Voltage

(V)

VIN

Logic Input Voltage VINH(min)/VINL(max)

(V)

VS or VD

Analog Voltage Range

(V)

20

- 20

2.4/0.8

± 20

15b

- 15

2.4/0.8

± 15

8c

- 8 (min)

2.4/0.8

± 8

相關PDF資料 |

PDF描述 |

|---|---|

| 5962-87700012A | PARALLEL, 8 BITS INPUT LOADING, 8-BIT DAC, CQCC20 |

| 5962-8770001EA | PARALLEL, 8 BITS INPUT LOADING, 8-BIT DAC, CDIP16 |

| 5962-8770002EX | PARALLEL, 8 BITS INPUT LOADING, 8-BIT DAC, CDIP16 |

| 5962-8770003EX | PARALLEL, 8 BITS INPUT LOADING, 8-BIT DAC, CDIP16 |

| 5962-8770101RX | DUAL, PARALLEL, 8 BITS INPUT LOADING, 8-BIT DAC, CDIP20 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 5962-8769002RA | 制造商:Advanced Micro Devices 功能描述: 制造商: 功能描述: 制造商:undefined 功能描述: |

| 5962-8769002SA | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| 5962-87692012A | 制造商:National Semiconductor Corporation 功能描述:Multiplexer 1-Element CMOS 3-ST 8-IN 20-Pin CLLCC 制造商:QP Semiconductor 功能描述:Multiplexer 1-Element CMOS 3-ST 8-IN 20-Pin CLLCC |

| 59628769201EA | 制造商:Texas Instruments 功能描述:54AC251DMQB |

| 5962-8769201EA | 制造商:QP Semiconductor 功能描述:MULTIPLEXER 1-ELEMENT CMOS 3-ST 8-IN 16-PIN CDIP |

發(fā)布緊急采購,3分鐘左右您將得到回復。