- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67320 > 5962-0053001HXC DUAL 1-CH 12-BIT PROPRIETARY METHOD ADC, SERIAL ACCESS, CQFP68 PDF資料下載

參數(shù)資料

| 型號: | 5962-0053001HXC |

| 元件分類: | ADC |

| 英文描述: | DUAL 1-CH 12-BIT PROPRIETARY METHOD ADC, SERIAL ACCESS, CQFP68 |

| 封裝: | CERAMIC, LCC-68 |

| 文件頁數(shù): | 3/20頁 |

| 文件大?。?/td> | 4809K |

| 代理商: | 5962-0053001HXC |

REV. A

AD13280

–11–

Power Supplies

Care should be taken when selecting a power source. Linear supplies

are strongly recommended. Switching supplies tend to have radiated

components that may be “received” by the AD13280. Each of

the power supply pins should be decoupled as closely as possible

to the package, using 0.1

F chip capacitors.

The AD13280 has separate digital and analog power supply

pins. The analog supplies are denoted AVCC and the digital

supply pins are denoted DVCC. AVCC and DVCC should be

separate power supplies because the fast digital output swings

can couple switching current back into the analog supplies.

Note that AVCC must be held within 5% of 5 V. The AD13280

is specified for DVCC = 3.3 V as this is a common supply for

digital ASICs.

Output Loading

Care must be taken when designing the data receivers for the

AD13280. The digital outputs drive an internal series resistor

(e.g., 100

) followed by a gate like 75LCX574. To minimize

capacitive loading, there should be only one gate on each output

pin. An example of this is shown in the evaluation board schematic

(Figure 9). The digital outputs of the AD13280 have a constant

output slew rate of 1 V/ns. A typical CMOS gate combined with

a PCB trace will have a load of approximately 10 pF. Therefore,

as each bit switches, 10 mA (10 pF

× 1 V ÷ 1 ns) of dynamic current

per bit will flow in or out of the device. A full-scale transition can

cause up to 120 mA (12 bits

× 10 mA/bit) of transient current

through the output stages. These switching currents are confined

between ground and the DVCC pin. Standard TTL gates should

be avoided since they can appreciably add to the dynamic switching

currents of the AD13280. It should also be noted that extra capacitive

loading will increase output timing and invalidate timing specifi-

cations. Digital output timing is guaranteed with 10 pF loads.

EVALUATION BOARD

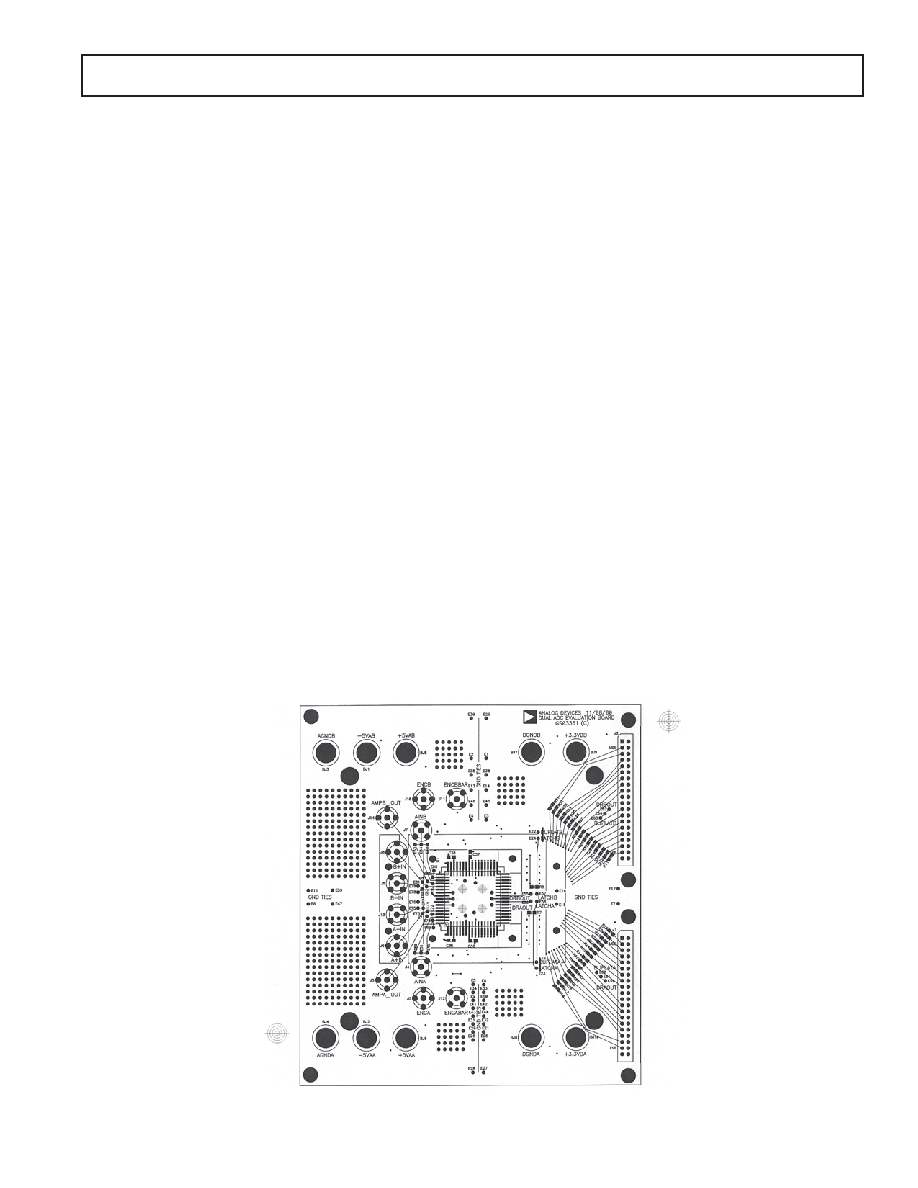

The AD13280 evaluation board (Figure 9) is designed to

provide optimal performance for evaluation of the AD13280

analog-to-digital converter. The board encompasses everything

needed to ensure the highest level of performance for evaluating

the AD13280. The board requires an analog input signal, encode

clock, and power supply inputs. The clock is buffered on-board

to provide clocks for the latches. The digital outputs and out

clocks are available at the standard 40-pin connectors J1 and J2.

Power to the analog supply pins is connected via banana jacks.

The analog supply powers the associated components and the

analog section of the AD13280. The digital outputs of the

AD13280 are powered via banana jacks with 3.3 V. Contact the

factory if additional layout or applications assistance is required.

LAYOUT INFORMATION

The schematics of the evaluation board (Figure

s 10a–10c) repre-

sent a typical implementation of the AD13280. The pinout of the

AD13280 is very straightforward and facilitates ease of use and

the implementation of high frequency/high resolution design prac-

tices. It is recommended that high quality ceramic chip capacitors

be used to decouple each supply pin to ground directly at the device.

All capacitors can be standard high quality ceramic chip capacitors.

Care should be taken when placing the digital output runs. Because

the digital outputs have such a high slew rate, the capacitive load-

ing on the digital outputs should be minimized. Circuit traces for

the digital outputs should be kept short and connect directly to

the receiving gate. Internal circuitry buffers the outputs of the

ADC through a resistor network to eliminate the need to exter-

nally isolate the device from the receiving gate.

Figure 9. Evaluation Board Mechanical Layout

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 5962-005300HXA | DUAL 1-CH 12-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

| 5962-005300HXX | DUAL 1-CH 12-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

| 5962-0150601HXX | DUAL 1-CH 14-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

| 5962-0251002HXC | 1-OUTPUT 8 W DC-DC REG PWR SUPPLY MODULE |

| 5962-9213902HZC | 1-OUTPUT 12 W DC-DC REG PWR SUPPLY MODULE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 5962005304899 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 5962005308115 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 5962005345643 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 5962-0053901QYA | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DIGITAL SIGNAL PROCESSOR |

| 5962-0053901QYC | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DIGITAL SIGNAL PROCESSOR |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。